# UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Estudio comparativo de los módulos UART, PWM, I2C, SPI y ADC entre los microcontroladores PIC16F887 y ATmega328P.

Trabajo de graduación presentado por Edgar Oliverio Fajardo Monzón para optar al grado académico de Licenciado en Ingeniería Mecatrónica

Guatemala,

# UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Estudio comparativo de los módulos UART, PWM, I2C, SPI y ADC entre los microcontroladores PIC16F887 y ATmega328P.

Trabajo de graduación presentado por Edgar Oliverio Fajardo Monzón para optar al grado académico de Licenciado en Ingeniería Mecatrónica

Guatemala,

Vo.Bo.:

Tribunal Examinador:

(f) Ing. Kurt Kellner

(f) \_\_\_\_\_\_M. Sc. José Eduardo Morales

(f) \_\_\_\_\_\_MAEB. Pablo Mazariegos

Fecha de aprobación: Guatemala, 3 de enero de 2023.

Prefacio

La programación de microcontroladores ha sido, desde que la conozco, mi área favorita de la Ingeniería Mecatrónica. Al haberme otorgado la oportunidad de desarrollar esta investigación, acepté sin dudarlo. No tengo duda alguna que fue una gran decisión, pues disfruté realizar la experimentación de la misma. Me siento orgulloso de haber aprendido un lenguaje de ensamblador distinto al que estoy habituado y poder aportar en el aprendizaje de los lectores.

Quiero agradecerle especialmente al Ingeniero Kurt Kellner, por la propuesta de investigación y la oportunidad de programar nuevamente en ensamblador. Una mención especial a mi colega y amigo Javier Schwendener, por acompañarme en este tema de investigación, complementando con los módulos faltantes.

Edgar Oliverio Fajardo Monzón Guatemala, 20 de diciembre de 2022.

# Índice general

| Prefac         | cio                                                                                                                                                                                                              | V              |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Índice         | e general                                                                                                                                                                                                        | IX             |

| Lista (        | de figuras                                                                                                                                                                                                       | XI             |

| Lista d        | de cuadros                                                                                                                                                                                                       | ΧV             |

| Resun          | nen                                                                                                                                                                                                              | XVI            |

| Abstra         | act                                                                                                                                                                                                              | XIX            |

| I I            | ntroducción                                                                                                                                                                                                      | 1              |

| II A<br>A<br>B | Antecedentes Comparación PIC vs AVR                                                                                                                                                                              |                |

| С              | dores                                                                                                                                                                                                            |                |

| III J          | ustificación                                                                                                                                                                                                     | 7              |

| А<br>В         | Objetivos Objetivo general                                                                                                                                                                                       |                |

| VI N           | Marco teórico                                                                                                                                                                                                    | 13             |

| A B C D E      | Generalidades de un microcontrolador  Puertos de entrada y salida $(I/O\ Ports)$ :  Oscilador:  Módulo temporizador $(Timer)$ :  Conversores de analógico a digital (ADC):  Modulación por ancho de pulso (PWM): | 13 13 13 14 14 |

| G              | Transmisor-Receptor asíncrono universal (UART):                                                                                                                                                                  | 14             |

| Η               | Interfaz periférica serial (SPI):                                           |

|-----------------|-----------------------------------------------------------------------------|

| I               | Circuito inter-integrado (I2C):                                             |

| J               | Microcontrolador PIC16F887                                                  |

| K               | ATmega328p                                                                  |

| L               | Analizador lógico                                                           |

| M               | Compilador                                                                  |

| N               | Lenguaje ensamblador                                                        |

| VII N           | Módulo Conversor Analógico a Digital (ADC)                                  |

| A               | Módulo ADC en PIC16F887                                                     |

|                 | 1 Registros y funcionamiento                                                |

|                 | 2 Selección del oscilador de conversión                                     |

|                 | 3 Lectura sin interrupción                                                  |

|                 | 4 Lectura con interrupción                                                  |

|                 | 5 Lectura de múltiples entradas                                             |

|                 | 6 Resumen de registros utilizados                                           |

| В               | Módulo ADC en ATmega328P                                                    |

|                 | 1 Registros y funcionamiento                                                |

|                 | 2 Selección del oscilador de conversión                                     |

|                 | 3 Lectura en modo de conversión única sin interrupción 25                   |

|                 | 4 Lectura en modo de conversión única con interrupción                      |

|                 | 5 Lectura en modo de corrida libre                                          |

|                 | 6 Lectura de múltiples entradas                                             |

|                 | Resumen de registros utilizados                                             |

| $^{\mathrm{C}}$ | Comparación módulos ADC: PIC16F887 y ATmega328P                             |

|                 | 1 Comparación de cantidad de instrucciones y tiempo de ejecución de códigos |

|                 | 2 Comparación de cantidad de registros utilizados por módulo 32             |

|                 |                                                                             |

| VIII            | Módulo de Modulación de Ancho de Pulso (PWM) 33                             |

| Α               | Módulo PWM en PIC16F887                                                     |

|                 | 1 Registros y funcionamiento                                                |

|                 | 2 Resumen de registros utilizados                                           |

| В               | Módulo PWM en ATmega328P                                                    |

|                 | 1 Registros y funcionamiento                                                |

|                 | 2 Cálculos de PWM                                                           |

|                 | 3 Código de ejemplo, Fast PWM normal                                        |

|                 | 4 Resumen de registros utilizados                                           |

| $^{\mathrm{C}}$ | Comparación módulos PWM: PIC16F887 y ATmega328P                             |

|                 | 1 Comparación de tamaño y tiempo de ejecución de códigos 40                 |

|                 | 2 Comparación de cantidad de registros utilizados por módulo 41             |

| IX N            | Módulo de Recepción y Transmisión Asíncrona Universal (UART) 43             |

| A               | Módulo UART en PIC16F887                                                    |

|                 | 1 Registros y funcionamiento                                                |

|                 | 2 Configuración y cálculo de Baudrate                                       |

|                 | 3 Envío de datos                                                            |

|                 | 4 Recepción de datos                                                        |

| B Módulo UART en ATmega328P                                                                              |                                               |                                                                      |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------|

| Envío de datos                                                                                           |                                               | 46                                                                   |

|                                                                                                          |                                               |                                                                      |

| 3 Recepción de datos                                                                                     |                                               | 48                                                                   |

|                                                                                                          |                                               | 48                                                                   |

| 4 Resumen de registros utilizados                                                                        |                                               | 49                                                                   |

| C Comparación módulos UART: PIC16F887 y ATmega328P                                                       |                                               | 49                                                                   |

| 1 Comparación cantidad de instrucciones y ciclos de reloj .                                              |                                               |                                                                      |

| 2 Comparación de cantidad de registros utilizados por módu                                               | ılo                                           | 53                                                                   |

| X Módulo de comunicación Interfaz Periférica Serial (SPI)                                                |                                               | ~ ~                                                                  |

| X Módulo de comunicación Interfaz Periférica Serial (SPI)  A Módulo MSSP, configuración SPI en PIC16F887 |                                               | <b>5</b> 5                                                           |

| 1 Comunicación por estándar SPI: Maestro                                                                 |                                               |                                                                      |

| 2 Comunicación por estándar SPI: Esclavo                                                                 |                                               |                                                                      |

| 3 Resumen de registros utilizados                                                                        |                                               |                                                                      |

| B Módulo SPI en ATmega328P                                                                               |                                               |                                                                      |

| 1 Comunicación por estándar SPI: Maestro                                                                 |                                               |                                                                      |

| 2 Comunicación por estándar SPI: Esclavo                                                                 |                                               |                                                                      |

| 1                                                                                                        |                                               |                                                                      |

| 3 Rosumon do rogistros utilizados                                                                        |                                               | 60                                                                   |

| 3 Resumen de registros utilizados                                                                        |                                               | 62                                                                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu                                                  | ulo SPI de                                    |                                                                      |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu<br>ATmega328P                                    | ulo SPI de                                    | 62                                                                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu                                                  | ulo SPI de                                    | 62                                                                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu<br>ATmega328P                                    | ulo SPI de ifaga                              | 62                                                                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu<br>ATmega328P                                    | ulo SPI de<br><br>ifaga                       | 62<br>63<br><b>67</b>                                                |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de  ifaga                             | 62<br>63<br><b>67</b><br>68                                          |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de<br><br>ifaga                       | 62<br>63<br><b>67</b><br>68<br>68                                    |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de ifaga                              | 62<br>63<br><b>67</b><br>68<br>68                                    |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de                                    | 62<br>63<br>67<br>68<br>68<br>71                                     |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de                                    | 62<br>63<br>67<br>68<br>68<br>71<br>75                               |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de  ifaga   ps, del AT-               | 62<br>63<br>67<br>68<br>68<br>71<br>75                               |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de                                    | 62<br>63<br>67<br>68<br>68<br>71<br>75<br>77                         |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de ifaga  ps, del AT-                 | 62<br>63<br>67<br>68<br>68<br>71<br>75<br>77<br>82                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | ulo SPI de ifaga  ps, del AT-                 | 62<br>63<br>67<br>68<br>68<br>71<br>75<br>77<br>82                   |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de afaga ps, del AT TWI com-          | 62<br>63<br>67<br>68<br>68<br>71<br>77<br>77<br>82<br>85             |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de  afaga  ps, del AT  TWI com-       | 62<br>63<br>67<br>68<br>68<br>71<br>75<br>77<br>82<br>85<br>85       |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de ifaga  ps, del AT  TWI com ifaga   | 62<br>63<br>67<br>68<br>68<br>71<br>77<br>77<br>82<br>85<br>86       |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de ifaga  ps, del AT  TWI com ifaga   | 62<br>63<br>67<br>68<br>68<br>71<br>75<br>77<br>82<br>85<br>85       |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de  afaga  ps, del AT  TWI com  afaga | 62<br>63<br>67<br>68<br>68<br>71<br>77<br>77<br>82<br>85<br>86       |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de ifaga  ps, del AT  TWI com- ifaga  | 62<br>63<br>68<br>68<br>71<br>77<br>77<br>82<br>85<br>86<br>89       |

| C Comparación módulos MSSP modo SPI de PIC16F887 y Módu ATmega328P                                       | alo SPI de  afaga  ps, del AT  TWI com  afaga | 62<br>63<br>68<br>68<br>71<br>75<br>77<br>82<br>88<br>88<br>88<br>89 |

# Lista de figuras

| 1  | Diagrama de pines del microcontrolador PIC16F887, empaquetado DIP de 40 pines              | 15      |

|----|--------------------------------------------------------------------------------------------|---------|

| 2  | Diagrama de pines del microcontrolador ATmega328P empaquetado DIP de 28 pines              | 16      |

| 3  | Comparación de tiempo de lecturas analógicas en ensamblador para PIC16F887 y ATmega328P    | 28      |

| 4  | Comparación de tiempo entre lecturas analógicas en ensamblador para PIC16F887 y ATmega328P | 7<br>29 |

| 5  | Comparación de tiempo de lecturas analógicas en C para PIC16F887 y AT-                     | 30      |

| 6  | Comparación de tiempo entre lecturas analógicas en C para PIC16F887 y                      | 30      |

| 7  | Comparación de respuesta del módulo PWM en ensamblador para PIC16F887 y ATmega328P         | 39      |

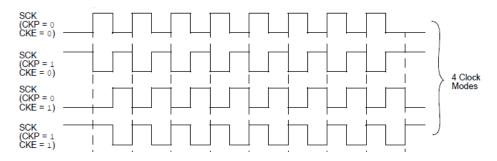

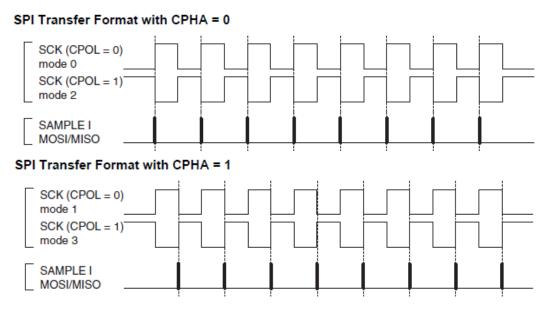

| 8  | Modos SPI según configuración del reloj. [11]                                              | 56      |

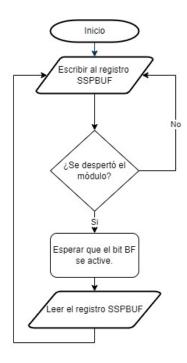

| 9  | Diagrama de flujo para comunicación por estándar SPI, rol maestro para PIC16F887           | 57      |

| 10 | Diagrama de flujo para comunicación por estándar SPI, rol esclavo para PIC16F887           | 58      |

| 11 | Modos SPI según configuración del reloj [12]                                               | 59      |

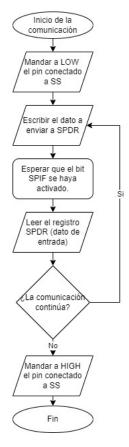

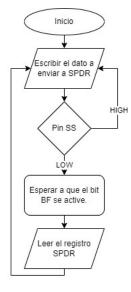

| 12 | Diagrama de flujo para comunicación por estándar SPI, rol maestro para ATmega328P          | 61      |

| 13 | Diagrama de flujo para comunicación por estándar SPI, rol esclavo para AT-                 | 61      |

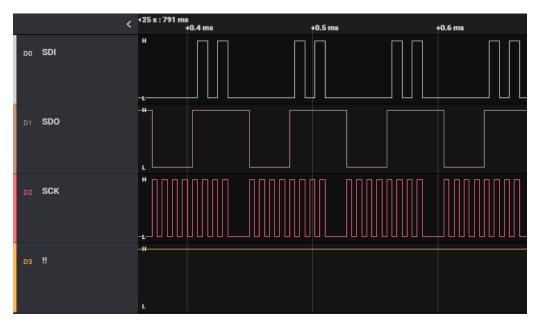

| 14 | Fragmento de señales de canales SDI, SDO, SCK y fallo, para comunicación                   | 63      |

| 15 |                                                                                            | 64      |

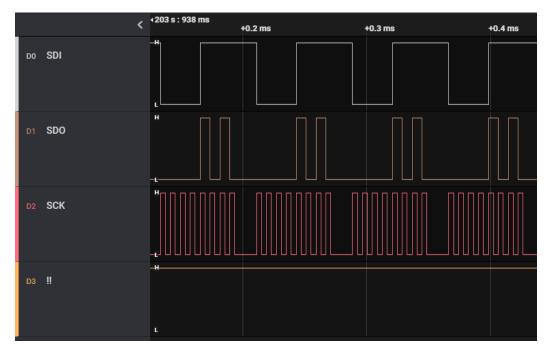

| 16 | Fragmento de señales de canales SDI, SDO, SCK y fallo, para comunicación                   | 64      |

| 17 |                                                                                            | 65      |

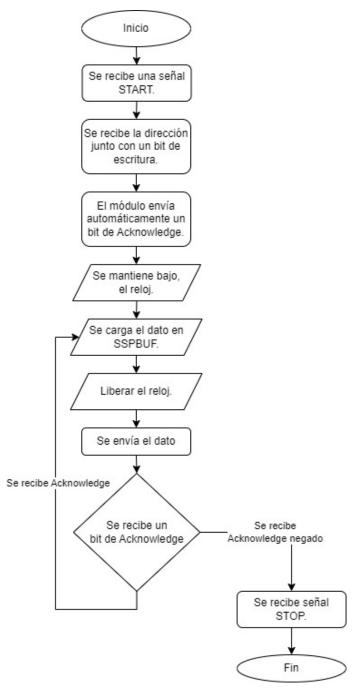

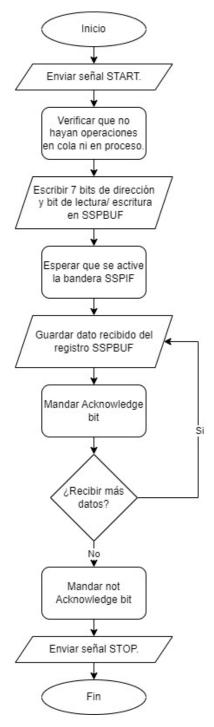

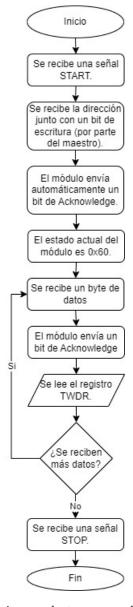

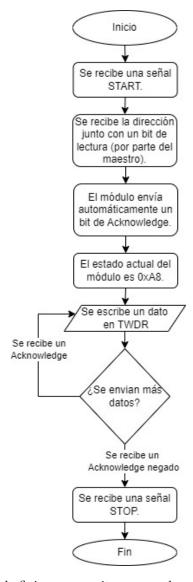

| 18 | Diagrama de flujo para escritura en esclavo I2C en PIC16F887               | 70 |

|----|----------------------------------------------------------------------------|----|

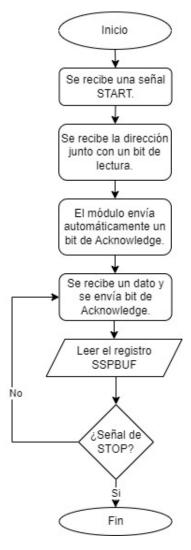

| 19 | Diagrama de flujo para lectura en esclavo I2C en PIC16F887                 | 71 |

| 20 | Diagrama de flujo para escritura en Maestro I2C en PIC16F887               | 74 |

| 21 | Diagrama de flujo para lectura en Maestro I2C en PIC16F887                 | 76 |

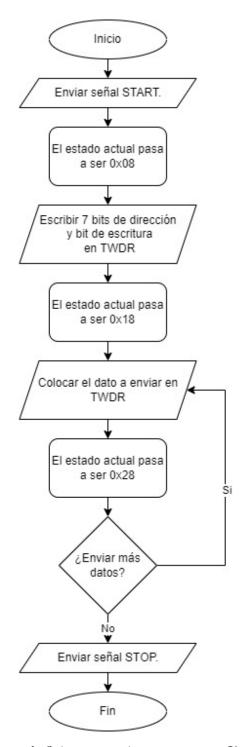

| 22 | Diagrama de flujo para escritura en maestro I2C en ATmega328P              | 80 |

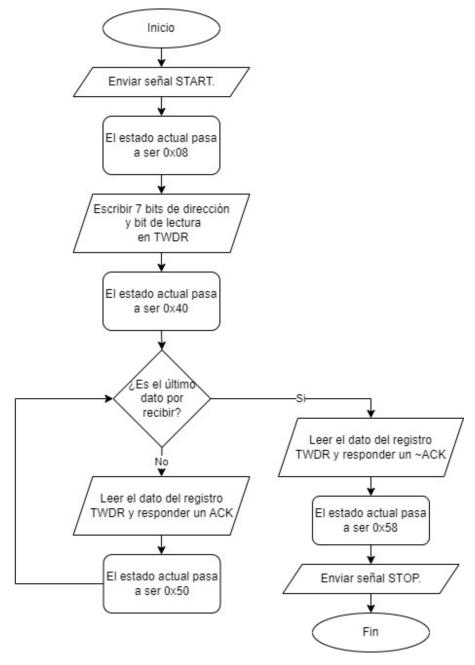

| 23 | Diagrama de flujo para lectura en maestro I2C en ATmega328P                | 81 |

| 24 | Diagrama de flujo para lectura en esclavo I2C en ATmega328P                | 83 |

| 25 | Diagrama de flujo para escritura en esclavo I2C en ATmega328P              | 84 |

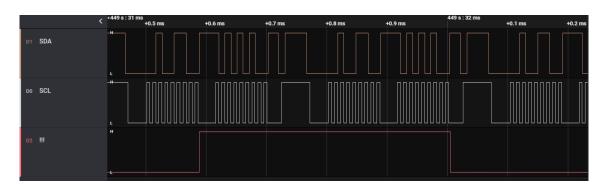

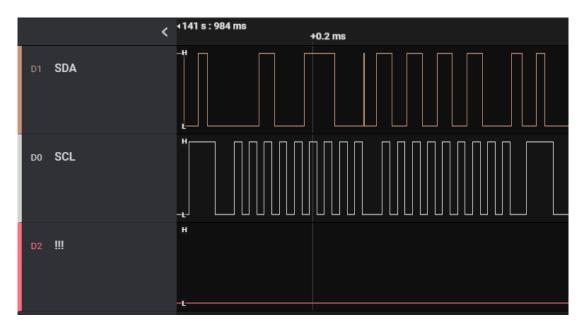

| 26 | Fragmento de señales en error, para canales SCK, SDA y fallo, comunicación |    |

|    | I2C en PIC16F887                                                           | 86 |

| 27 | Vista completa de señal de fallo para comunicación I2C en PIC16F887        | 86 |

| 28 | Fragmento de señales en canales SCK, SDA y fallo para comunicación I2C en  |    |

|    | PIC16F887                                                                  | 87 |

| 29 | Vista completa de señal de fallo para comunicación I2C en ATmega<br>328P   | 87 |

|    |                                                                            |    |

# Lista de cuadros

| 1  | Canal analógico correspondiente a cada pin para registro ANSEL                  |    |

|----|---------------------------------------------------------------------------------|----|

| 2  | Canal analógico correspondiente a cada pin para registro ANSELH                 | 18 |

| 3  | Tiempos de adquisición según el rango de conversión, utilizando oscilador       |    |

|    | principal                                                                       | 18 |

| 4  | Tiempos de adquisición según el voltaje de alimentación, utilizando oscilador   |    |

|    | dedicado del módulo ADC.                                                        | 19 |

| 5  | Configuraciones disponibles para selección de oscilador de ADC                  | 19 |

| 6  | Cálculos de tiempo de adquisición según frecuencia de reloj                     | 19 |

| 7  | Registros utilizados para el módulo ADC en PIC16F887                            | 23 |

| 8  | Selección de referencia en ATmega328P                                           | 24 |

| 9  | Selección de frecuencia de oscilador de conversión                              | 24 |

| 10 | Cálculo de frecuencias del oscilador de conversión según prescaler para 16 MHz  | 25 |

| 11 | Cálculo de frecuencias del oscilador de conversión según prescaler para 8 MHz   | 25 |

| 12 | Resumen de registros utilizados en el módulo ADC en ATmega328P                  | 28 |

| 13 | Conteo de instrucciones en la configuración del ADC y periodos de reloj to-     |    |

|    | tales utilizados en PIC16F887, según programa propuesto, en ensamblador         | 30 |

| 14 | Conteo de instrucciones en la ejecución del ADC y periodos de reloj totales     |    |

|    | utilizados en PIC16F887, seún programa propuesto, en ensamblador                | 31 |

| 15 | Conteo de instrucciones en la configuración del ADC y ciclos de instrucción     |    |

|    | totales utilizados en ATmega328P, según programa propuesto, en ensamblador.     | 31 |

| 16 | Conteo de instrucciones en la ejecución del ADC y ciclos de instrucción totales |    |

|    | utilizados en ATmega328P, según programa propuesto, en ensamblador              | 31 |

| 17 | Comparación ciclos de reloj para ADC en ensamblador                             | 32 |

| 18 | Comparación cantidad de instrucciones necesarias para configuración y eje-      |    |

|    | cución del módulo ADC en ensamblador.                                           | 32 |

| 19 | Comparación de cantidad de registros utilizados por módulo                      | 32 |

| 20 | Salidas del canal 1 de PWM mejorado                                             | 33 |

| 21 | Modos del canal 1 de PWM mejorado                                               | 34 |

| 22 | Registros utilizados en el módulo PWM en PIC16F887                              | 35 |

| 23 | Canales y pines correspondientes                                                |    |

| 24 | Configuración canal A de PWM 0                                                  | 36 |

| 25 | Configuración canal B de PWM 0                                                  | 36 |

| 26 | Funciones del módulo                                                            |    |

| 27 | Selección de reloj para módulo PWM                                                                                                                     | 36  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 28 | Registros utilizados en el módulo PWM en ATmega328p                                                                                                    | 39  |

| 29 | Medición de error de frecuencias obtenidas de los PWM de ambos microcon-                                                                               |     |

|    | troladores                                                                                                                                             | 40  |

| 30 | Conteo de instrucciones en la configuración del PWM y periodos de reloj                                                                                |     |

|    | totales utilizados en PIC16F887, según programa propuesto en ensamblador                                                                               | 40  |

| 31 | Conteo de instrucciones en el cambio del ciclo de trabajo del PWM y perio-                                                                             |     |

|    | dos de reloj totales utilizados en PIC16F887, según programa propuesto en                                                                              | 4.0 |

| 00 | ensamblador                                                                                                                                            | 40  |

| 32 | Conteo de instrucciones en la configuración del PWM y ciclos de instrucción                                                                            | 40  |

| 99 | totales utilizados en ATmega328P, según programa propuesto en ensamblador.                                                                             | 40  |

| 33 | Conteo de instrucciones en el cambio del ciclo de trabajo del PWM y ciclos de instrucción totales utilizados en ATmega328P, según programa propuesto   |     |

|    | en ensamblador                                                                                                                                         | 41  |

| 34 | Comparación ciclos de reloj para PWM en ensamblador                                                                                                    | 41  |

| 35 | Comparación de cantidad de instrucciones necesarias para configuración y                                                                               | 11  |

| 00 | ejecución del módulo PWM en ensamblador                                                                                                                | 41  |

| 36 | Comparación de cantidad de registros utilizados por módulo                                                                                             | 42  |

|    |                                                                                                                                                        |     |

| 37 | Ecuaciones para configuración del baudrate en PIC16F887                                                                                                |     |

| 38 | Registros utilizados en el módulo UART en PIC16F887                                                                                                    |     |

| 39 | Modos disponibles del módulo UART                                                                                                                      | 47  |

| 40 | Configuraciones para modificar tamaño de carácter                                                                                                      | 47  |

| 41 | configuración de Bit de paridad                                                                                                                        | 47  |

| 42 | Ecuaciones para cálculo del registro UBRRO                                                                                                             | 48  |

| 43 | Registros utilizados en el módulo UART en PIC16F887                                                                                                    | 49  |

| 44 | Conteo de instrucciones en la configuración de la recepción de datos para                                                                              |     |

|    | UART y periodos de reloj totales utilizados en PIC16F887, según programa                                                                               | 50  |

| 45 | propuesto, en ensamblador                                                                                                                              | 50  |

| 45 | terrupciones y conteo de periodos de reloj utilizados en PIC16F887, según                                                                              |     |

|    | programa propuesto, en ensamblador                                                                                                                     | 50  |

| 46 | Conteo de instrucciones en la configuración de transmisión de datos por UART                                                                           | 00  |

| 10 | y periodos de reloj totales utilizados en PIC16F887, según programa propues-                                                                           |     |

|    | to, en ensamblador                                                                                                                                     | 50  |

| 47 | Conteo de instrucciones en la transmisión de datos por UART y periodos de                                                                              |     |

|    | reloj totales utilizados en PIC16F887, según programa propuesto, en ensam-                                                                             |     |

|    | blador                                                                                                                                                 | 51  |

| 48 | Conteo de instrucciones en la configuración de recepción de datos en UART y                                                                            |     |

|    | ciclos de instrucción utilizados en ATmega328P, según programa propuesto,                                                                              |     |

|    | en ensamblador                                                                                                                                         | 51  |

| 49 | Conteo de instrucciones para recepción de datos en UART utilizando inte-                                                                               |     |

|    | rrupciones y conteo de ciclos de instrucción utilizados en ATmega328P, según                                                                           | ۲.  |

| EO | programa propuesto, en ensamblador                                                                                                                     | 51  |

| 50 | Conteo de instrucciones para configuración de transmisión de datos en UART y ciclos de instrucción utilizados en ATmega328P, según programa propuesto, |     |

|    | en ensamblador                                                                                                                                         | 51  |

| 51 | Conteo de instrucciones para transmisión de datos en UART y ciclos de instrucción utilizados en ATmega328P, según programa propuesto, en ensambla- |    |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|    | dor.                                                                                                                                               | 52 |

| 52 | Comparación ciclos de reloj para UART en ensamblador                                                                                               | 52 |

| 53 | Comparación de cantidad de instrucciones necesarias para configuración y                                                                           |    |

|    | ejecución del módulo UART según programas propuestos en ensamblador                                                                                | 52 |

| 54 | Comparación de cantidad de registros utilizados por módulo                                                                                         | 53 |

| 55 | Configuración de bits SSPM [3:0] para SPI                                                                                                          | 56 |

| 56 | Configuración de registros TRISx según el rol asignado para configuración                                                                          |    |

|    | SPI en PIC16F887                                                                                                                                   | 57 |

| 57 | Registros utilizados en el módulo MSSP: configuración SPI                                                                                          | 58 |

| 58 | Configuración de la señal de reloj para el módulo SPI de ATmega328P                                                                                | 59 |

| 59 | Configuración de registro DDRB según el rol asignado para configuración SPI                                                                        |    |

|    | en ATmega328P                                                                                                                                      | 60 |

| 60 | Registros utilizados para el estándar SPI en ATmega328P                                                                                            | 62 |

| 61 | Registros utilizados para la configuración y ejecución del estándar SPI en                                                                         |    |

|    | microcontroladores PIC16F887 y ATmega328P                                                                                                          | 62 |

| 62 | Señales de indicación para comunicación I2C                                                                                                        | 67 |

| 63 | Configuración de bits SSPM[3:0] para I2C                                                                                                           |    |

| 64 | Registros utilizados en el módulo MSSP: configuración I2C                                                                                          |    |

| 65 | Códigos de estado para maestro en transmisión                                                                                                      |    |

| 66 | Códigos de estado para maestro en recepción                                                                                                        |    |

| 67 | Códigos de estado para esclavo en recepción                                                                                                        | 82 |

| 68 | Códigos de estado para esclavo en transmisión                                                                                                      | 82 |

| 69 | Registros utilizados en el módulo TWI (I2C)                                                                                                        |    |

| 70 | Registros utilizados para la configuración y ejecución de la comunicación I2C                                                                      |    |

|    | en microcontroladores PIC16F887 y ATmega328P                                                                                                       | 85 |

Resumen

En la Universidad del Valle de Guatemala se imparte el curso de Programación de Microcontroladores y Electrónica Digital 2 haciendo uso del microcontrolador PIC16F887. El mismo utiliza el PICkit3 o PICkit4, los cuales presentan una serie de dificultades en cuanto a su configuración y uso. Se propone como alternativa a este microcontrolador el uso del ATmega328P, el cual es utilizado en la plataforma de desarrollo Arduino UNO.

Con el propósito de determinar la mejor opción para la enseñanza en la Universidad del Valle de Guatemala, se compara el rendimiento del microcontrolador PIC16F887 con el microcontrolador ATmega328P, esto por medio de analizadores lógicos y ciclos de reloj utilizados; las tareas realizadas son las propuestas en el curso de Programación de Microcontroladores en los laboratorios que involucran los módulos ADC, PWM, UART, I2C y SPI. Los módulos se programaron en ambos microcontroladores tanto en lenguaje ensamblador, como en C, exceptuando los módulos I2C y SPI, los cuales son programados únicamente en C.

Este estudio nos muestra mejores resultados en el ADC del ATmega328P a comparación del módulo ADC del PIC16f887, el cual tiene una resolución muy variable y lecturas más lentas así como un mayor tiempo antes de iniciar una nueva lectura. El resultado se repite en ambos lenguajes de programación, aumentando evidentemente en C. En los protocolos de comunicación evaluados, el comportamiento es equivalente y la cantidad de registros modificados depende del microcontrolador, requiriendo menos el ATmega328P.

**Abstract**

Universidad del Valle de Guatemala (UVG) teaches courses on programming of microcontrollers, those courses uses the PIC16F887 microcontroller. This one need the PicKit3 or PicKit4 tool, both have trouble configuring and using. It is proposed as an alternative to PIC16F887, to use ATmega328P microcontroller. This is the same as the used in Arduino UNO board.

In order to determine the best option to teach in UVG, the performance is compared in both microcontrollers, using logic analyzers and machine cycles required in programs. The suggested ADC, PWM, UART, I2C and SPI programs from Programming of microcontrollers course are used to develop this investigation. Modules are programmed in both microcontrollers in Assembly language and C, except I2C and SPI, that are programmed only in C.

This investigation shows better results in the ADC Module of ATmega328P than PIC16F887, the last one shows less precision and longer resolution times as well longer times to restart a conversion. This situation continues in C language, getting longer times for both devices but even longer with PIC16F887. The performance of evaluated communication protocols are equivalent and the number of used registers depends on the microcontroller, with ATmega328P using less resgisters.

# CAPÍTULO

Introducción

La programación de microcontroladores es un área fundamental en carreras relacionadas con la electrónica, se debe en gran medida a la utilidad de los microcontroladores para realizar tareas especificas con circuitos. Una buena forma de iniciar la enseñanza de programación de microcontroladores es con dispositivos de pocos bits. Siendo de esta forma muy común iniciar con dispositivos *Midrange* entre los cuales se pueden encontrar una amplia variedad de dispositivos de 8 bits.

La Universidad del Valle de Guatemala adoptó al PIC16F887 para impartir el curso de Programación de Microcontroladores y Electrónica Digital 2. Evaluando una mejor opción para impartir dichos cursos, se propone el ATmega328P. Tomando en cuenta el rendimiento, por medio de analizadores lógicos y ciclos de máquina utilizados en cada programa.

El estudio comparativo abarca los módulos ADC, PWM, UART, I2C y SPI; para los microcontroladores PIC16F887 y ATmega328P. Las tareas que deben completar estos módulos son basadas en las prácticas sugeridas del curso de Programación de Microcontroladores de la UVG. Para realizar una comparación justa se procura realizar el programa mínimo viable para el funcionamiento de la tarea solicitada, con el objetivo de mantener los ciclos de máquina y tiempos de respuesta en mínimos.

El estudio incluye el funcionamiento de los módulos, así como los registros involucrados con el mismo. Además, de características relevantes de cada módulo y características extras, útiles para la implementación, como interrupciones del módulo. La comparación se realiza en la parte final de cada capitulo, comparando con el analizador lógico, en los casos que lo amerita, las comparaciones y tiempos de respuesta de ambos microcontroladores; y comparando los ciclos de máquina según las instrucciones ejecutadas en los programas.

Antecedentes

El PIC16F887 es un microcontrolador utilizado en la Universidad del Valle de Guatemala para enseñanza de arquitectura de computadoras y lenguajes de programación como Assembler y C. [1] En universidades como Gujarat Technology University, se utiliza la familia de microcontroladores PIC18 [2] y en universidades como el Massachusets Institute of Technology (MIT), se utiliza la familia AVR, específicamente el ATmega328p. Cabe resaltar que este microcontrolador es el integrado en la plataforma Arduino UNO. [3]

A continuación se describen trabajos relacionados a la comparación de Microcontroladores de 8 bits.

# A. Comparación PIC vs AVR

Limor Fried, realizó una publicación en su foro personal en el año 2004. Esta publicación compara microcontroladores de AVR contra PIC, en esta investigación evalúa puntos importantes de cada familia de microcontroladores [4].

Fried evalúa varios aspectos en su análisis. Se toma en cuenta el precio, los lenguajes de programación y compiladores para cada familia. Evalúa los entornos de desarrollo (IDE), así como los kits de desarrollo, facilidad para principiantes en programación de microcontroladores y caracteristicas especiales propias de cada familia.

La publicación presenta una comparación de microcontroladores de capacidades comparables y de la misma cantidad de pines. Evalúa los PIC 12F629, 16F628 y 18F452 contra ATtiny13, ATtiny2313 y ATmega32 respectivamente. Llegando a la conclusión que los precios de estos son similares, por lo que para los microcontroladores evaluados, no existía realmente una diferencia elevada de precios. La comparación de los assembler para ambas familias concluye en la eficiencia de instrucciones para AVR, así como la mejor calidad en cuanto a compilador de AVR para programación en C.

Posteriormente, evalúa los entornos de desarrollo para los cuales en ese momento, no era superior ninguno, puesto que ambos cuentan con soporte solo para Windows.

Se contrastan los kits de desarrollo de ambas familias, para PIC se expone el Pickit1 con un precio de 44\$ en el año 2004 y para AVR se presenta el STK500 con un precio de 80\$, concluyendo como mejor opción el Pickit1 por el precio. Finalmente se analiza cual de las 2 familias es más viable para un principiante, con los 2 exponentes respectivos, siendo los mismos Arduino para AVR y BASIC Stamp para PIC, debido a la facilidad que presenta Arduino, introduciendo C con macros para facilitar el aprendizaje, se le determina como superior en este aspecto.

# B. Syllabus de universidades para enseñanza de programación de microcontroladores

Para la enseñanza de programación de microcontroladores en otras universidades del mundo se utilizan microcontroladores de la familia PIC como de la familia AVR, de la misma forma que existen universidades más centradas en la enseñanza de la arquitectura para un mejor entendimiento, utilizando otras plataformas de desarrollo, por lo que se presentan las siguientes universidades con sus respectivos cursos.

Gujarat Technological University, proporciona el curso de *PIC Microcontroller and embebed systems* [2]. En el que se enseña a programar en PIC para procesamiento de señales y programación de sensores, motores, relés, entre otros. En este curso se enseña el desarrollo de programas en C para el microcontrolador PIC18, abarcan también la arquitectura RISC para el mismo.

Massachusetts Institute of Technology utiliza el ATMega328p en la placa de microcontrolador Arduino Uno, para proporcionar el curso de *PERFORMANCE ENGINEERING OF SOFTWARE SYSTEMS* [3], se enseña assembler para AVR así como arquitectura del microcontrolador. El curso se orienta a aprender como mejorar el rendimiento de los programas por medio del conocimiento del conocimiento profundo de la plataforma.

La Texas Tech University (TTU), imparte el curso de *Microcontrollers*[5], utilizando el microcontrolador MSP430 de Texas Instruments, en el mismo se enseña Assembler y C. Se introducen los conceptos de subrutinas, interrupciones y funciones del microcontrolador. Además, en esta Universidad se enseña la arquitectura RISC en el curso *Microprocessor Architecture* [6], en el que se diseña un procesador sencillo basado en la arquitectura RISC (arquitectura empleada en el ATmega328p).

University of Alabama (UA), se imparte el curso *Microcomputers* [7], utilizando el microcontrolador PIC24, para el cual se enseña la arquitectura interna del microcontrolador, direccionamiento de memoria y modos de direccionamiento. Impartiendo assembler y C para el mismo.

En la Universidad del Valle de Guatemala se imparte el curso de Programación de Microcontroladores [1] utilizando el microcontrolador PIC16F887. El curso instruye arquitecturas de microcontroladores, además de fundamentos de assembler para PIC, en el curso se exponen las diferentes funciones del microcontrolador y la implementación de las mismas. El mismo microcontrolador se utiliza en Electrónica digital 2[8] para programar en C así como la TIVA C TM4C123G de Texas Instruments.

#### C. Comparación de arquitecturas de 8 bits

En el año 1997, Microchip realizó una comparación de microcontroladores de 8 bits contra los PIC16C5X/XX [9]. En la investigación se compararon rendimiento y tiempo de ejecución de la misma tarea. Los microcontroladores comparados fueron: SGS-Thomson ST62 8 MHz, Motorola MC68HC05 4.2 MHz, Intel 8051 20 MHz, Zilog Z86CXX 12 MHz, National COP800 20 MHz

Se realizó una comparación del tiempo de ejecución para realizar la codificación de un byte, Loop control, comprobación de bit y direccionamiento, así como introducción de un byte en un registro y configuración del reloj, configuración de un timer. En la investigación se obtiene el promedio de tamaño de código por microcontrolador obteniendo 1.29 para el COP 800, 2.10 para el ST62, 2.24 para el MC68HC05, 1.51 para Z86CXX, 1.547 para el 8051 y finalmente 1.00 para el PIC16C5X/XX. Para los tiempos de ejecución relativos se obtienen los siguientes resultados, 0.108 para el COP 800, 0.0455 para el ST62, 0.136 para el MC68HC05, 0.212 para Z86CXX, 0.30 para el 8051 y finalmente 1.00 para el PIC16C5X/XX debido a que es el punto de comparación. Concluyendo con que el menor tamaño de código es el PIC16C5X/XX y de la misma forma en tiempos de ejecución relativos, siendo el PIC16C5X/XX el más rápido y el de mayor tiempo de ejecución es el ST62.

# CAPÍTULO III

Justificación

La programación y conocimiento de arquitecturas de microcontroladores es un aspecto fundamental en múltiples ramas de la ingeniería. Mejorar el rendimiento de los programas requiere conocer los microcontroladores y manejar sus respectivos lenguajes ensambladores. Es la razón por la cual muchas universidades en el mundo enseñan estos aspectos en sus cursos de microcontroladores.

La Universidad del Valle de Guatemala emplea el microcontrolador PIC16F887 en cursos como Programación de Microcontroladores y Electrónica Digital 2, además de una introducción a lenguajes de ensamblador en Electrónica Digital 1. La programación de estos dispositivos ha presentado problemas, por ejemplo, de programación con el PICkit 3. Adicionalmente el costo es más elevado que otros microntroladores y no está tan ampliamente disponible.

El objetivo de este trabajo de graduación es evaluar otro candidato disponible localmente. Este candidato es el ATmega328p utilizado en las plataformas de desarrollo Arduino UNO, el cual presenta una mayor disponibilidad en nuestra región, además de un costo inferior.

Por lo mencionado con anterioridad, se pretende realizar una comparación en términos generales de ambos microcontroladores para determinar la viabilidad de la implementación del mismo en los cursos mencionados, en la Universidad del Valle de Guatemala.

# CAPÍTULO IV

Objetivos

### A. Objetivo general

Realizar un estudio comparativo entre los microcontroladores PIC16F887 y ATmega328P, de los módulos ADC, PWM, I2C, SPI y UART, y evaluar los parámetros necesarios para determinar la mejor opción para la enseñanza de microcontroladores en la Universidad del Valle de Guatemala.

# B. Objetivos específicos

- Comparar el rendimiento del microcontrolador PIC16F887 con el microcontrolador Atmega328p por medio de analizadores lógicos, evaluando los módulos: ADC, PWM, I2C, SPI y UART.

- Realizar los laboratorios y proyectos propuestos en el curso de Programación de Microncontroladores de la Universidad del Valle de Guatemala, relacionados a los módulos a evaluar, en ambos microcontroladores.

# capítulo V

Alcance

Este estudio abarca la comparación y funcionamiento externo y de configuración de los módulos ADC, PWM, UART, I2C y SPI de los microcontroladores ATmega328P y PIC16F887, programados mediante la herramienta PicKit4. Procurando obtener los programas óptimos para cada uno, más no es el objetivo principal hallar estos programas mínimos viables. El estudio utiliza el compilador XC8 de Microchip para ambos microcontroladores utilizando tanto el assembler de PIC (PIC-AS) como el assembler de AVR (AVRASM2). Para compilación en C es utilizado el compilador base MPLAB XC8 C.

El estudio analiza únicamente la programación y rendimiento de los microcontroladores de forma externa. No se pretende indagar en la arquitectura de los mismos ni se abarca el comportamiento de los microcontroladores expuestos a diferentes condiciones ambientales, esto incluye temperaturas, voltajes y campos eléctricos o magnéticos.

Marco teórico

#### A. Generalidades de un microcontrolador

Un microcontrolador es un circuito integrado programable. [10] Los mismos son utilizados para la fabricación de sistemas embebidos. Estos cuentan generalmente con una memoria flash, RAM, ALU, EEPROM, oscilador (algunos modelos antiguos de microcontroladores, no incluyen oscilador y se debe colocar un oscilador externo), entradas y salidas; las funciones incluidas en el microcontrolador, dependen del modelo, como lo podrían ser módulos de Timer, Conversores analógico a digital (ADC), módulos de PWM, así como módulos de comunicación bajo diferentes protocolos, como UART, I2C o SPI [11].

# B. Puertos de entrada y salida $(I/O \ Ports)$ :

Estos son todas las entradas y salidas con capacidad de recibir o emitir un dato digital, es decir un voltaje HIGH o LOW, entre el rango definido. [10] Los microcontroladores manejan estos datos de forma binaria siendo clasificados por el microcontrolador dependiendo de los rangos de voltajes establecidos.

#### C. Oscilador:

Módulo fundamental para el funcionamiento del microcontrolador, este determina la frecuencia de operación del mismo. En algunos casos, este es programable para determinar diferentes frecuencias de operación [10]. Las formas de programar el mismo dependen según el microcontrolador. En otras ocasiones este módulo es remplazado por osciladores externos conocidos también como cristales.

#### D. Módulo temporizador (Timer):

Este módulo depende del fabricante, sin embargo, por lo general estos funcionan como contadores de aumento, para el cual al alcanzar un número determinado activan interrupciones en el programa. Pueden tener funciones extras como la captura y comparación de datos en tiempo, así como pre-escalados [11]. Los mismos pueden llegar a ser utilizados en otros módulos o activar interrupciones para realizar una tarea de forma periódica.

# E. Conversores de analógico a digital (ADC):

Estos módulos permiten la conversión de una señal de entrada analógica a a una salida binaria. La cantidad de bits utilizada para la representación de dicha señal dependen de la resolución de conversión utilizada por el módulo [12]. La comparación de voltaje se realiza generalmente al voltaje de operación del microcontrolador, sin embargo, existen algunos módulos con comparación ajustable para otros voltajes [11].

### F. Modulación por ancho de pulso (PWM):

Este módulo modifica el ciclo de trabajo de un pulso periódico, con el objetivo de controlar la cantidad de energía que se envía, o bien, transmitir información [13]. Estos módulos generalmente tienen pines vinculados a estos módulos y suelen estar ligados a los módulos de timer así como una forma de control analógico controlado digitalmente.

# G. Transmisor-Receptor asíncrono universal (UART):

Es un protocolo de comunicación para el intercambio de datos entre 2 dispositivos, este protocolo utiliza 2 canales que son para recibir y transmitir [14]. Esta comunicación puede ser Simplex, Semiduplex o duplex. Siendo unidireccional, bidireccional por turnos o bidireccional simultánea [11].

# H. Interfaz periférica serial (SPI):

Es un protocolo de comunicación que utiliza como máximo 4 canales: CS, MISO, MOSI y SCK. Estos son para seleccionar el chip, para recepción del maestro, para la emisión del maestro y para control del reloj respectivamente [15].

# I. Circuito inter-integrado (I2C):

Es un protocolo de comunicación serial, este protocolo permite la comunicación de 2 dispositivos digitales por medio del uso de 2 canales, los cuales constan de data y reloj (SDA y SCL)[15].

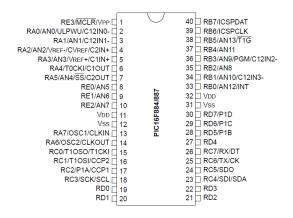

#### J. Microcontrolador PIC16F887

Es un microcontrolador de 8 bits, de la familia PIC, desarrollado por Microchip, con 40/44 pines dependiendo del empaquetado del mismo, basado en Flash y posee una arquitectura Harvard modificada. El PIC16F887 tiene una longitud de palabra de 14 bits. Este microcontrolador posee los siguientes modulos: Oscilador, 3 módulos de timer, de los cuales 2 son de 8 bits y 1 de 16 bits; cuenta con un módulo comparador, un módulo ADC de 13 canales, 2 canales de PWM, módulo de comunicación UART, un módulo MSSP que incluye I2C y SPI [11].

Figura 1: Diagrama de pines del microcontrolador PIC16F887, empaquetado DIP de 40 pines.

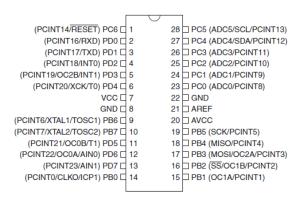

# K. ATmega328p

Es un microcontrolador de 8 bits basado en AVR RISC, desarrollado por Atmel, actualmente propiedad de Microchip. Cuenta con 28/32 pines dependiendo del empaquetado, tiene una longitud de palabra de 16 bits. Este microcontrolador posee los siguientes módulos: 6 canales PWM, 3 módulos de timer, de los cuales 2 son de 8 bits y uno de 16 bits, 6 canales ADC con resolución máxima de 10 bits, un módulo comparador, módulo de comunicación UART, un módulo de comunicación SPI y un módulo de programación I2C [12].

Figura 2: Diagrama de pines del microcontrolador ATmega328P empaquetado DIP de 28 pines.

#### L. Analizador lógico

Es un instrumento utilizado para capturar datos en un sistema digital con el objetivo de depurar errores en circuitos y verificar el funcionamiento de los mismos monitorizando el voltaje en los nodos conectados. Permitiendo visualizar el estado de diferentes señales digitales simultáneamente. Esta herramienta permite verificar el tiempos de subida o bajada, estados lógicos y cambios de estado [16].

# M. Compilador

La compilación se refiere a la conversión de un algoritmo expresado en un lenguaje humano a un algoritmo expresado en lenguaje de máquinas, por lo que el compilador traduce el código en un lenguaje hacia lenguaje de máquina previo a su implementación [17].

# N. Lenguaje ensamblador

Es un lenguaje de bajo nivel, el cual es aún legible por un humano, este tiene la intención de comunicarse de forma casi directa al hardware del microcontrolador, generalmente traducido a lenguaje de máquina con el uso de un compilador. Este utiliza instrucciones básicas que se ejecutan en cierta cantidad de ciclos de máquina dependiendo de la instrucción y el dispositivo en el que se ejecuta. El lenguaje de ensamblador que se utiliza puede variar entre cada dispositivo dependiendo de su fabricante [18].

# Módulo Conversor Analógico a Digital (ADC)

Tanto el PIC16F887, como el ATmega328P; cuentan con un módulo ADC que permite la conversión de una señal analógica a una señal digital. Se comparan ambos módulos en función del tiempo de conversión con las mismas configuraciones y la cantidad de registros que se modifican. Se realiza el programa en ensamblador y C para ambos microcontroladores. El logic analyzer se configura para que lea los datos a 125 MS/s, por 500 ms. A continuación se explica el módulo ADC de ambos microcontroladores.

### A. Módulo ADC en PIC16F887

### 1. Registros y funcionamiento

El módulo posee un multiplexor (MUX) de 13 entradas analógicas. La selección de la entrada deseada, se realiza en el registro A/D CONTROL REGISTER 0 (ADCON0), en los bits [3:0]. Se puede seleccionar los pines con entrada analógica del Puerto A [5], [3:0]; del puerto E [2:0] y del puerto B [5:0]. Para los cuales, el pin o los pines a utilizar tienen que estar establecidos como entradas, utilizando el registro TRISx, correspondiente al puerto que se va a utilizar. Es necesario verificar el canal analógico del pin a utilizar, tal como se presenta en el Cuadro 1 y 2, modificando los registros ANSEL y ANSELH¹.

| PIN             | A0   | A1   | A2   | A3   | A5   | E0   | E1   | E2   |

|-----------------|------|------|------|------|------|------|------|------|

| Canal analógico | ANS0 | ANS1 | ANS2 | ANS3 | ANS4 | ANS5 | ANS6 | ANS7 |

Cuadro 1: Canal analógico correspondiente a cada pin para registro ANSEL.

$<sup>^1\</sup>mathrm{Importante}$  notar que los canales analógicos del registro ANSELH, no se encuentran en el mismo orden de los pines.

| PIN             | B2   | В3   | B1    | B4    | В0    | B5    |

|-----------------|------|------|-------|-------|-------|-------|

| Canal analógico | ANS8 | ANS9 | ANS10 | ANS11 | ANS12 | ANS13 |

Cuadro 2: Canal analógico correspondiente a cada pin para registro ANSELH.

Al momento de activar un bit de ANSEL o ANSELH, se activa la resistencia pull-up interna de forma automática para el pin seleccionado. Además de activar el canal analógico correspondiente.

El resultado de la conversión tiene una resolución de 10 bits que se almacenan en los registros ADRESH y ADRESL. La "justificación" del resultado puede ser hacia la izquierda o hacia la derecha, esto significa que el bit más significativo (msb), se encuentra en el msb del registro ADRESH para el caso de justificación izquierda. En caso contrario, es decir en caso de justificación derecha, el bit menos significativo (lsb), se encuentra en lsb del registro ADRESL. Para seleccionar uno de los dos casos de justificación, se debe modificar el bit ADFM del registro ADCON1, es decir el bit 7 de dicho registro. Por defecto, el microcontrolador selecciona la justificación izquierda, con el valor 0 en el bit ADFM. El registro ADCON1, puede modificar a su vez, los voltajes de referencia para la comparación del ADC, mediante los registros VCFG1 y VCFG0, conectando las referencias necesarias a los pines A2 y A3. La modificación de referencias son útiles para sensores que requieren niveles de voltaje diferentes a 5v.

Para iniciar el módulo se puede utilizar el bit ADON del registro ADCON0, este registro se puede activar en cualquier momento de la configuración de estos registros. El bit  $\mathrm{GO}/\overline{DONE}$ , en cambio, se activa únicamente al momento de iniciar la conversión, este se activa posteriormente a finalizar la configuración.

### 2. Selección del oscilador de conversión

El PIC16F887, tiene un requisito de tiempo de adquisición de datos  $(T_{AD})$ , según la hoja de datos del PIC, este tiempo varía en función de los voltajes de referencia, contando con los tiempos presentados en el Cuadro 3. Estos tiempos de adquisición no son válidos para el oscilador dedicado del módulo ADC, para el cual, se utilizan los  $(T_{AD})$  que se presentan en el Cuadro 4. Para el oscilador dedicado los valores varían en función del voltaje de alimentación  $(V_{DD})$ , del PIC<sup>2</sup>.

| $V_{Ref}$    | Min                 | Max       |

|--------------|---------------------|-----------|

| ≥ 3.0V       | $1.6~\mu\mathrm{S}$ | $9 \mu S$ |

| Rango entero | $3 \mu S$           | $9 \mu S$ |

Cuadro 3: Tiempos de adquisición según el rango de conversión, utilizando oscilador principal.

$<sup>^{2}</sup>$ Este oscilador depende del voltaje de alimentación del PIC, el mismo puede variar entre  $160 \mathrm{KHz}$  y  $500 \mathrm{KHz}$

| $V_{DD}$ | Min                 | Típico    | Max       |

|----------|---------------------|-----------|-----------|

| 2.5V     | $3 \mu S$           | $6 \mu S$ | $9 \mu S$ |

| 5V       | $1.6~\mu\mathrm{S}$ | $4 \mu S$ | $6 \mu S$ |

Cuadro 4: Tiempos de adquisición según el voltaje de alimentación, utilizando oscilador dedicado del módulo ADC.

Una conversión requiere  $11 T_{AD}$ , por lo que se tiene que cumplir los requisitos presentados en los cuadros 3 y 4.

El microcontrolador cuenta con 4 configuraciones, entre las cuales escoger la frecuencia del oscilador para la conversión. Las configuraciones se presentan en el Cuadro 5, estas se seleccionan con los bits ADCS [1:0], del registro ADCONO. Se puede obtener el tiempo de adquisición a partir de la frecuencia del oscilador seleccionado y aplicando el prescaler a dicha frecuencia, el periodo del resultado presenta el tiempo de adquisición. Este mismo se compara contra los límites de  $T_{AD}$ .

| Selección de oscilador | ADCS |

|------------------------|------|

| $F_{OSC}/2$            | 00   |

| $F_{OSC}/8$            | 01   |

| $F_{OSC}/32$           | 10   |

| Oscilador dedicado     | 11   |

Cuadro 5: Configuraciones disponibles para selección de oscilador de ADC.

| $F_{OSC}$ | Prescaler    | $F_{Res}$ | T (s)                 | T (μs) | Válido |

|-----------|--------------|-----------|-----------------------|--------|--------|

|           | $F_{OSC}/2$  | 10 MHz    | $1 \times 10^{-7}$    | 0.1    | No     |

| 20MHz     | $F_{OSC}/8$  | 2.5 MHz   | $4 \times 10^{-7}$    | 0.4    | No     |

|           | $F_{OSC}/32$ | 625 KHz   | $1.6 \times 10^{-6}$  | 1.6    | Sí     |

|           | $F_{OSC}/2$  | 8 MHz     | $1.25 \times 10^{-7}$ | 0.125  | No     |

| 16MHz     | $F_{OSC}/8$  | 2 MHz     | $5 \times 10^{-7}$    | 0.5    | No     |

|           | $F_{OSC}/32$ | 500 KHz   | $2 \times 10^{-6}$    | 2      | Sí     |

|           | $F_{OSC}/2$  | 4 MHz     | $2.5 \times 10^{-7}$  | 0.25   | No     |

| 8MHz      | $F_{OSC}/8$  | 1 MHz     | $1 \times 10^{-6}$    | 1      | No     |

|           | $F_{OSC}/32$ | 250 KHz   | $4 \times 10^{-6}$    | 4      | Sí     |

|           | $F_{OSC}/2$  | 2 MHz     | $5 \times 10^{-7}$    | 0.5    | No     |

| 4MHz      | $F_{OSC}/8$  | 500 KHz   | $2 \times 10^{-7}$    | 2      | Sí     |

|           | $F_{OSC}/32$ | 125 KHz   | $8 \times 10^{-6}$    | 8      | Sí     |

| 1MHz      | $F_{OSC}/2$  | 500 KHz   | $2 \times 10^{-6}$    | 2      | Sí     |

|           | $F_{OSC}/8$  | 125 KHz   | $8 \times 10^{-6}$    | 8      | Sí     |

|           | $F_{OSC}/32$ | 31250Hz   | $3.2 \times 10^{-5}$  | 32     | No     |

Cuadro 6: Cálculos de tiempo de adquisición según frecuencia de reloj.

### 3. Lectura sin interrupción

Se debe completar la configuración del módulo modificando los registros ADCON0 y ADCON1, posterior a este proceso, se puede iniciar la conversión AD con el bit  $GO/\overline{DONE}$  del registro ADCON0, se debe monitorizar que la conversión se complete, por lo que se debe esperar que se cumpla alguna de las dos siguientes condiciones: El bit GO se limpia o el bit ADIF del registro PIR1 se activa. El resultado se mantiene en los registros ADRESH y ADRESL.

```

CONF:

BANKSEL ANSEL

MOVLW

0b00010000

;Canal analógico 12 activo

MOVWF

ANSELH

BANKSEL TRISB

MOVLW

;Seleccionar el PBO como entrada

0b0000001

MOVWF

TRISB

BANKSEL PORTA

MOVLW

0b01110001

;Selecciona el oscilador Fosc/8 [7:6], canal 12 [5:2]

MOVWF

ADCONO

;y se activa el módulo ADC [0]

BSF

ADCONO, 1

;Inicia la conversión

READ:

BTFSS

PIR1, 6

;Se verifica el estado del bit ADIF

GOTO

$-1

MOVF

ADRESH, W

;Se lee el registro ADRESH

MOVWF

adcValue

;Se guarda en una variable

BCF

PIR1, 6

;Se limpia la bandera de conversión AD

BSF

ADCONO, 1

;Inicia la conversión

GOTO

READ

```

La selección del oscilador se realiza tomando en cuenta la frecuencia del oscilador interno utilizado en el programa, por defecto el PIC16F887 utiliza el reloj interno de 4MHz, por lo que las configuraciones disponibles según los cálculos presentados en el Cuadro 6. Por lo que se selecciona la frecuencia de conversión más rápida.

### 4. Lectura con interrupción

Cuando se cuenta con interrupción, no es necesario monitorizar la conversión. Para activar las interrupciones es necesario activar los bits GIE y PIE del registro INTCON, en el caso específico de la interrupción para el ADC, se debe activar el bit ADIE del registro PIE1. Además de la necesidad de guardar los valores actuales al momento de entrar al vector de interrupción. La bandera ADIF se debe de limpiar al finalizar las operaciones de la interrupción y antes de la instrucción RETFIE. El vector de interrupción es el 0x0004, por lo que se debe colocar las instrucciones a ejecutar a partir de este espacio de memoria, cuando se tiene activa más de una interrupción es necesario verificar la interrupción.

```

PSECT intVect, class=CODE, delta=2

ORG 0x0004

SAVE:

MOVWF

;Guardamos W en una variable

w_temp

STATUS, W

SWAPF

MOVWF

s_temp

;Guardamos STATUS

INT:

BTFSS

PIR1, 6

;Se comprueba si la interrupción es de ADC (ADIF)

GOTO

LOAD

MOVF

ADRESH, W

;Se lee el resultado de la conversión

MOVWF

adcValue

PIR1, 6

BCF

;Se limpia la bandera ADIF

BSF

ADCONO, 1

;Se inicia la conversión nuevamente

LOAD:

SWAPF

s_temp, W

MOVWF

STATUS

;Se regresa STATUS

SWAPF

w_temp, F

SWAPF

w_temp, W

;Se regresa W

RETFIE

```

Como se demuestra en el código, se guarda STATUS y de W, además de regresarlo al finalizar. Se verifica el estado de la bandera ADIF y posterior a comprobarlo, guarda el resultado en una variable. Por último, limpia el estado de la bandera de interrupción para poder repetir el programa.

```

CONF:

BANKSEL ANSEL

MOVLW

0b00010000

;Canal analógico 12 activo

MOVWF

ANSELH

BANKSEL TRISB

MOVLW

0b00000001

;Selecciona el puerto PBO como entrada

MOVWF

TRISB

;Se activan GIE Y PIE

MOVLW

0b11000000

MOVWF

INTCON

MOVLW

0b01000000

;Se activan las interrupciones por ADC (ADIE)

MOVWF

PIE1

BANKSEL PORTA

MOVLW

0b01110001

;Selecciona el oscilador Fosc/8 [7:6], canal 12 [5:2]

MOVWF

ADCONO

;y se activa el módulo ADC [0]

;Inicia la conversión

BSF

ADCONO, 1

```

### 5. Lectura de múltiples entradas

Para realizar lecturas con múltiples entradas, se debe cambiar el canal en el registro ADCONO. Esto se debe realizar posterior a finalizar la conversión. Se puede realizar sin importar si se realizan interrupciones. Para asegurar el tiempo necesario de descarga del capacitor interno del módulo, se recomienda realizar el cambio de canal posterior a leer el resultado de la conversión.

```

INT:

PIR1, 6

BTFSS

;Se comprueba si la interrupción es de ADC (ADIF)

GOTO

LOAD

MOVLW

01110001

SUBWF

ADCONO, W

BTFSS

STATUS, 2

;Se verifica el canal actual

GOTO

CH10

MOVF

ADRESH, W

;Se lee el resultado de la conversión

MOVWF

adcValue1

;Se guarda en variable de lectura 1

GOTO

SWITCH

CH10:

MOVF

ADRESH, W

;Se lee el resultado de la conversión

MOVWF

adcValue2

;Se guarda en variable de lectura 2

SWITCH:

MOVLW

00011000

XORWF

ADCONO

;alterna de canal, sin modificar los demás valores

BCF

PIR1, 6

;Se limpia la bandera ADIF

BSF

ADCONO, 1

;Se inicia la conversión nuevamente

```

Se recomienda en Ensamblador, si se utilizan solo 2 canales, calcular un *Exclusive Or* (XOR). Pues esta operación permite alternar entre 2 canales con 2 instrucciones, sin modificar la configuración establecida previamente, además, que la misma máscara utilizada para cambiarlo de canal, sirve para revertir la operación. En este ejemplo, el cambio de canal se realiza en la sección de código "SWITCH", para modificar el canal utilizado.

```

CONF:

BANKSEL ANSEL

MOVLW Ob00010100 ;Seleccionamos los canales 12 y 10

MOVWF ANSELH

BANKSEL TRISB

MOVLW Ob00000011 ;Activamos las entradas de los pines PBO Y PB1

MOVWF TRISB

BANKSEL PORTA

```

MOVLW Ob01110001

MOVWF ADCONO

BSF ADCONO, 1 ;Iniciamos la conversión

En esta ocasión, al utilizar 2 canales, se deben activar ambos en el registro de ANSELH correspondientes a sus canales; así como los pines utilizados como entradas analógicas.

### 6. Resumen de registros utilizados

| Registro | Usos                                                                 |

|----------|----------------------------------------------------------------------|

| ANSEL    | Estos activan los puertos analógicos de los 14 disponibles.          |

| ANSELH   | Estos activan los puertos analogicos de los 14 disponibles.          |

|          | Este registro permite la selección del canal a utilizar, la          |

| ADCON0   | señal de reloj que utiliza el módulo y activar el módulo, así        |

|          | como iniciar una conversión.                                         |

| ADCON1   | El registro permite justificar el resultado a la derecha o izquierda |

| ADCONI   | y establecer las referencias a utilizar.                             |

Cuadro 7: Registros utilizados para el módulo ADC en PIC16F887

# B. Módulo ADC en ATmega328P

### 1. Registros y funcionamiento

El módulo posee un MUX de 6 canales en el caso del empaquetado DIP, los cuales se pueden seleccionar mediante los bits MUX[3:0] del registro ADMUX. Se pueden seleccionar los pines con entrada analógica del Puerto C [5:0]. Para los cuales se debe configurar los pines a utilizar como entradas, con el registro DDRC, limpiando el bit correspondiente al pin; y activar las resistencias Pull-up, con el registro PORTC activando el bit correspondiente al pin a utilizar<sup>3</sup>.

El resultado de la conversión tiene una resolución de 10 bits que se almacena en los registros ADCH y ADCL. La "justificación" del resultado puede ser hacia la izquierda o hacia la derecha, esto significa que el bit más significativo (msb), se encuentra en el msb del registro ADCH para el caso de justificación izquierda. En caso contrario, es decir en caso de justificación derecha, el bit menos significativo (lsb), se encuentra en lsb del registro ADCL. Para seleccionar uno de los dos casos de justificación, se debe modificar el bit ADLAR del registro ADMUX, es decir el bit 5 de dicho registro. Por defecto, el ATmega328P, está configurado para estar jusficado a la derecha, con el valor 0 del bit ADLAR. El registro ADMUX configura los voltajes de referencia con los bits REFS1 Y REFS0 del registro ADMUX[7:6]; las configuraciones de estos bits se pueden ver en el Cuadro 8 <sup>4</sup>.

<sup>&</sup>lt;sup>3</sup>Es importante para activar la resistencia Pull-up, que el bit PUD del registro MCUCR se encuentre limpio, de lo contrario, se desactivaran las resistencias Pull-up internas.

<sup>&</sup>lt;sup>4</sup>Tanto la selección 01 como 11, necesitan un capacitor en el pin AREF

| REFS[1:0] | $V_{ref}$                   |

|-----------|-----------------------------|

| 00        | Referencia en pin AREF      |

| 01        | Referencia en pin $AV_{CC}$ |

| 10        | Sin uso                     |

| 11        | Referencia de 1.1V          |

Cuadro 8: Selección de referencia en ATmega328P.

Para iniciar el módulo se puede utilizar el bit ADEN del registro ADCSRA, este bit activa el oscilador seleccionado con los bits ADPS[2:0] del registro ADCSRA[2:0], los factores de prescaler se presentan en el Cuadro 9.

| ADPS[2:0] | Prescaler |

|-----------|-----------|

| 000       | 2         |

| 001       | 2         |

| 010       | 4         |

| 011       | 8         |

| 100       | 16        |

| 101       | 32        |

| 110       | 64        |

| 111       | 128       |

Cuadro 9: Selección de frecuencia de oscilador de conversión.

### 2. Selección del oscilador de conversión

El oscilador se debe de seleccionar dependiendo del modo que se selecciona en los bits ADTS[2:0] del registro ADCSRB, únicamente cuando se activa el modo de activación automática *Auto Trigger* con el bit ADATE del registro ADCSRA. A continuación se presenta ambos modos de conversión.

### Conversión única

En modo de conversión única, el prescaler que se selecciona solo afecta la velocidad de la conversión, la resolución del resultado es siempre de 10 bits. En este modo solo es necesario activar el bit ADSC del registro ADCSRA, el cual se limpia al finalizar la conversión, esto activa a su vez el bit ADIF<sup>5</sup> del registro ADCSRA. Las conversiones en este modo se interrumpen hasta que la bandera se limpia y se vuelve a activar el bit ADSC.

<sup>&</sup>lt;sup>5</sup>Esta bandera se activa independiente del estado de las interrupciones, con interrupciones activas o desactivadas.

### Conversión de corrida libre

En modo de corrida libre, la frecuencia del oscilador afecta la resolución del resultado, de forma en la que independientemente del prescaler seleccionado, la conversión ocurre, para garantizar 10 bits de resolución en este modo, se debe de conseguir una frecuencia entre 50kHz y 200kHz, como se muestra en los cuadros 10 y 11, las combinaciones que logran esto con 8MHz, son los prescalers 128 y 64. Si se utilizan osciladores externos, se debe de verificar el cumplimiento mínimo de dicha frecuencia para garantizar 10 bits de resolución.

| Prescaler | Frecuencia resultante | $T(\mu s)$ | 10 bits de resolución |

|-----------|-----------------------|------------|-----------------------|

| 2         | 8 MHz                 | 0.125      | NO                    |

| 4         | 4 MHz                 | 0.25       | NO                    |

| 8         | 2 MHz                 | 0.5        | NO                    |

| 16        | 1 MHz                 | 1          | NO                    |

| 32        | 500 kHz               | 2          | NO                    |

| 64        | 250 kHz               | 4          | NO                    |

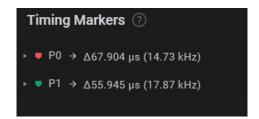

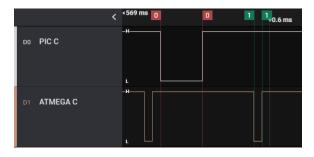

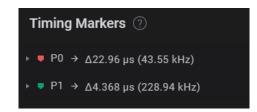

| 128       | 125 kHz               | 8          | SÍ                    |