## UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Diseño de un circuito integrado con tecnología 180 nm usando librerías de diseño de TSMC: Automatización de la etapa de síntesis lógica y creación de archivos Verilog para pruebas físicas en un FPGA Genesys Xilinx Virtex-5 LX50T y automatización de la verificación extracción de parásitos.

Trabajo de graduación presentado por Allison Estuardo Aguilar Chocooj para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala,

## UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Diseño de un circuito integrado con tecnología 180 nm usando librerías de diseño de TSMC: Automatización de la etapa de síntesis lógica y creación de archivos Verilog para pruebas físicas en un FPGA Genesys Xilinx Virtex-5 LX50T y automatización de la verificación extracción de parásitos.

Trabajo de graduación presentado por Allison Estuardo Aguilar Chocooj para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala,

Vo.Bo.:

(f) Ing. Jonathan de los Santos

Tribunal Examinador:

Ing. Jonathan de los Santos

(f) \_\_\_\_\_\_ MSc. Carlos Esquit

(f) \_\_\_\_\_\_Ing. Luis Nájera

Fecha de aprobación: Guatemala, 20 de Junio de 2023.

Prefacio

El método de enseñanza se orienta a la investigación y el desarrollo de tecnologías que buscan solucionar problemas de la población. La ingeniería electrónica que se imparte en la Universidad del Valle de Guatemala abarca la electrónica digital como la electrónica analógica, sin embargo, marcan la diferencia en la enseñanza y aplicación de cada una de estas dos ramas de la electrónica. Este proyecto no es solo la unión de estas dos disciplinas, abarca el diseño y fabricación de circuitos integrados en una disciplina más compleja que se integra en la industria. En el diseño de un circuito integrado a escala nano métrica es de vital importancia que un ingeniero electrónico maneje y domine las herramientas de software para la correcta creación en cada etapa de un circuito integrado. La empresa IMEC es colaboradora del diseño y fabricación del primer chip en Guatemala, con lo que nos proporcionó todos los recursos necesarios, tanto software como las restricciones y librerías de TSMC para poder llevar a cabo el diseño.

Este trabajo, que se ha realizado a lo largo de varios años, consta de dos etapas de flujo de diseño para circuitos integrados, estas son: Síntesis lógica y síntesis física. Para ambas etapas se cuenta con documentación de los pasos a seguir, así para una mejor comprensión en el uso de las herramientas de Synopsys.

Para la síntesis lógica se escaló de forma que se inició con un circuito de muy baja complejidad y se escaló en complejidad para luego poder sintetizar estos circuitos. Se comienza con una compuerta lógica NOT, luego una compuerta lógica XOR, luego un Sumador Completo, luego una unidad aritmética lógica y un contador secuencial de 4 bits.

Para la síntesis física se comenzó utilizando la herramienta de IC Compiler I y se hizo un gran avance al actualizar a IC Compiler II, con esta mejora de proceso se presentaron desafíos, ya que al actualizar no se tiene conocimiento de correcto manejo de esta herramienta con las actualizaciones que tiene, pero se contó con el apoyo de documentación y trabajos anteriores y el apoyo importante del IMEC para terminar este diseño. A esta etapa de síntesis física le sigue etapas de verificaciones que tienen que cumplir con los requerimientos de dichas pruebas para poder cumplir con las reglas de manufactura que solicita TSMC, con esto se le hace las verificaciones de LVS, LPE, ERC, Antenna y Rule Check. Al pasar cada una de estas comprobaciones, el circuito propuesto es apto para ser fabricado.

Debido a la complejidad, el trabajo en equipo entre los demás miembros de esta investigación es fundamental y juega un papel importante. No solo en la delegación de tareas y el logro de objetivos individuales, sino también para lograr el objetivo general, que en colaboración con la UVG es la creación del primer circuito a nano escala de la región.

# Índice

| Prefacio Pre | V   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Lista de figuras                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | X   |

| Lista de cuadros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | XI  |

| Resumen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XIV |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XV  |

| . Introducción                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1   |

| 2. Antecedentes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3   |

| 2.1 Instalación de aplicaciones de Synopsys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5   |

| 2.2 Generación de archivo Verilog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5   |

| 2.3 Síntesis lógica                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 2.4 Síntesis Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5   |

| 2.5 Síntesis Cell_IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 2.6 Síntesis física                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| 2.7 Comprobaciones físicas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7   |

| 3. Justificación                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13  |

| I. Objetivos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15  |

| 4.1 Objetivo general                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15  |

| 4.2 Objetivos específicos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15  |

| 5. Alcance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17  |

| 6. Marco teórico                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 19  |

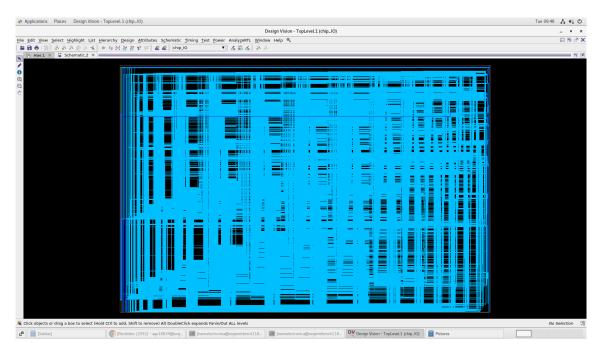

| 6.1 Design Vision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 19  |

| 6.2 VCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

| 6.3 Scripting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20  |

| 6.4 StarRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22  |

| 6.4.1 Características de StarRC                                                  | 22 |

|----------------------------------------------------------------------------------|----|

| 6.4.2 Flujo de diseño de StarRC                                                  | 23 |

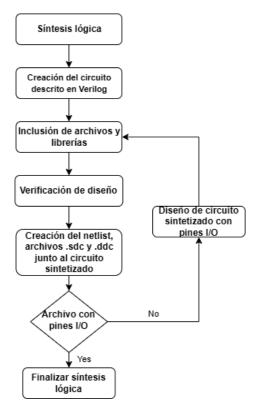

| 6.5 Síntesis lógica                                                              | 23 |

| 6.5.1 Flujo del diseño                                                           | 23 |

| 7. Script de Python para lectura universal                                       | 25 |

| 7.1 Código explicado                                                             | 26 |

| 8. Planificación de la automatización                                            | 33 |

| 8.1 Script de BASH                                                               | 33 |

| 8.1.2 Resultados del script                                                      | 33 |

| 8.2 Script para Design Compiler                                                  | 36 |

| 8.2.1 Inclusión de librerías                                                     | 36 |

| 8.2.2 Revisión de diseño                                                         | 38 |

| 8.2.3 Compilación                                                                | 39 |

| 8.2.4 Reportes                                                                   | 39 |

| 8.2.5 Outputs                                                                    | 39 |

| 9. Modificaciones importantes de archivos                                        | 41 |

| 9.1 Modificación del texto                                                       | 41 |

| 9.2 Modificación del contador                                                    | 45 |

| 9.3 Modificación de la tabla de verdad                                           | 46 |

| 10.Integración de la automatización con la etapa de síntesis física y extracción |    |

| de parásitos                                                                     | 49 |

| 10.1 Montar servidor compartido                                                  | 49 |

| 10.2 Script modificado para uso dentro del servidor                              | 51 |

| Integración de extracción de parásitos                                           | 52 |

| 11. Automatización de la verificación de extracción de parásitos                 | 55 |

| 11.1 Script para la automatización de la verificación                            | 55 |

| 12.Conclusiones                                                                  | 61 |

| 13. Recomendaciones                                                              | 63 |

|                                                                                  |    |

| 14.Bibliografía                                                                  | 65 |

| 15.Anexos                                                                        | 67 |

| 15.1 Códigos útiles y de resultados                                              | 67 |

# Lista de figuras

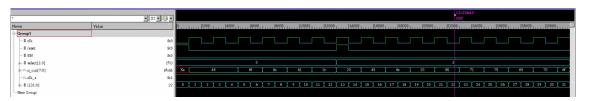

| 1.                | Comportamiento del nanoChip                                                     | 5  |

|-------------------|---------------------------------------------------------------------------------|----|

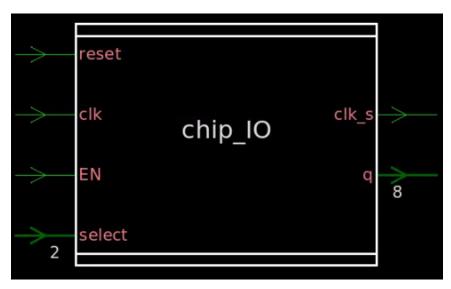

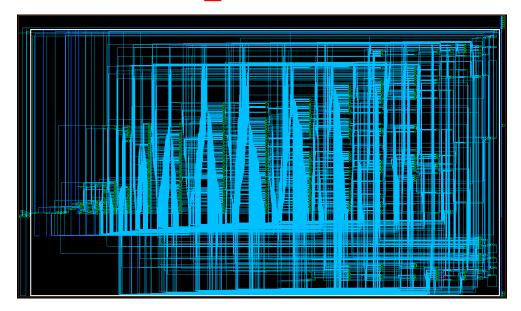

| 2.                | Esquemático del nanoChip                                                        | 6  |

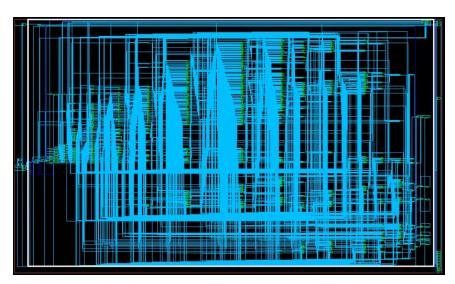

| 3.                | Core del nanoChip                                                               | 6  |

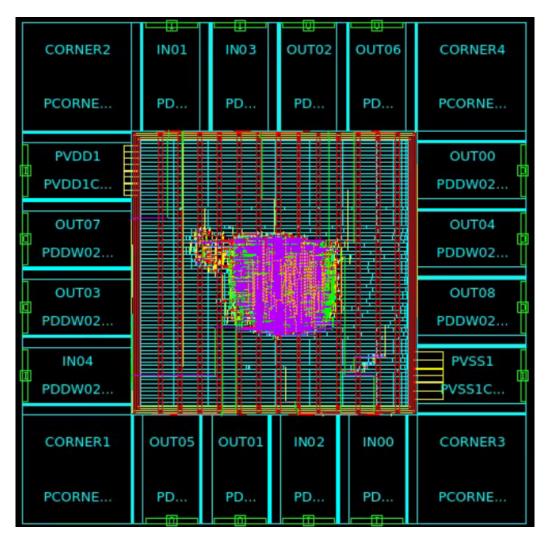

| 4.                | Core del nanoChip                                                               | 7  |

| 5.                | DRC mostrando NOT CLEAN                                                         | 8  |

| 6.                | DRC mostrando errores en la densidad de los 6 metales                           | 9  |

| 7.                | Verificación de Antenna                                                         | 10 |

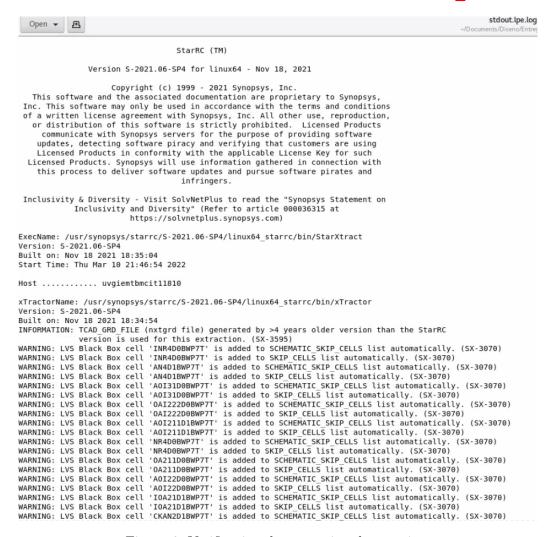

| 8.                | Verificación de extracción de parásitos                                         | 11 |

|                   |                                                                                 |    |

| 9.                | Flujo de diseño de StarRC                                                       | 23 |

| 10.               | Diagrama del flujo de diseño                                                    | 24 |

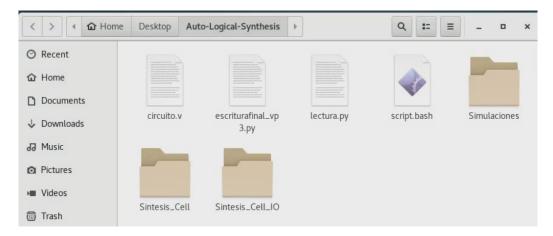

| 11.               | Carpeta ubicada en el escritorio                                                | 34 |

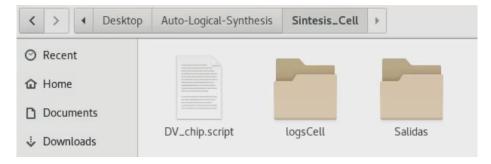

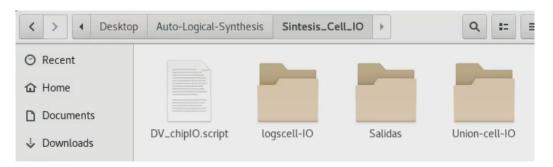

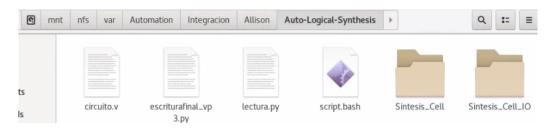

| $\frac{11.}{12.}$ | Archivos dentro de Sintesis Cell                                                | 34 |

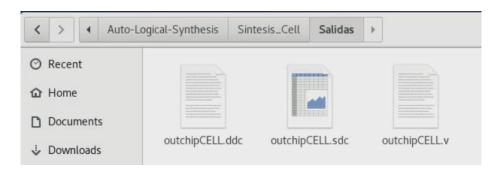

| 12.<br>13.        | Archivos de salida dentro de la carpeta de salidas                              | 34 |

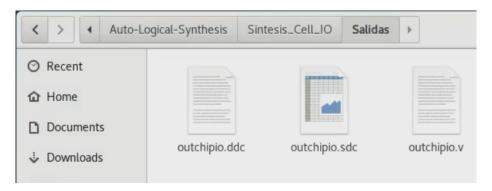

| 14.               | Archivos de Sanda dentro de la Carpeta de Sandas                                | 35 |

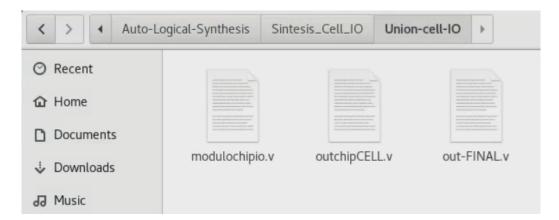

| 15.               | Archivos dentro de Union-cell-IO                                                | 35 |

| 16.               | Archivos de salida con pines de entrada y salida dentro de la carpeta de salida |    |

| 10.               | Tremvos de sanda con pines de entrada y sanda dentro de la carpeta de sanda     | 90 |

| 17.               | Estructura de la lógica combinacional del texto anterior                        | 42 |

| 18.               | Estructura de la lógica combinacional del texto nuevo que es utiliza            | 45 |

|                   |                                                                                 |    |

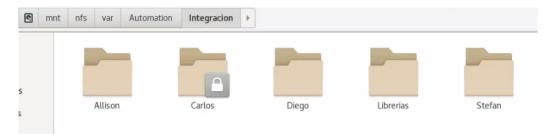

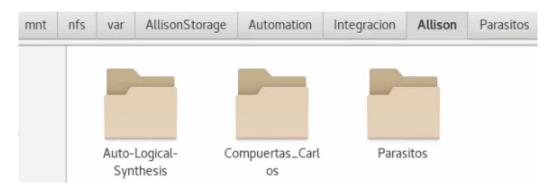

| 19.               | Carpetas dentro del servidor compartido                                         | 50 |

| 20.               | Carpetas contenidas dentro de la sección designada                              | 50 |

| 21.               | Automatización de síntesis lógica                                               | 51 |

| 22.               | Automatización de extracción de parásitos                                       | 52 |

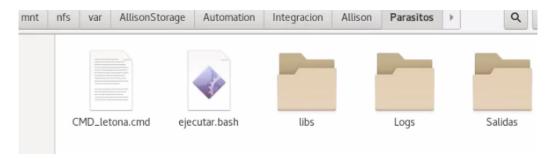

| 23.               | Dentro de la carpeta de parásitos dentro del servidor compartido                | 52 |

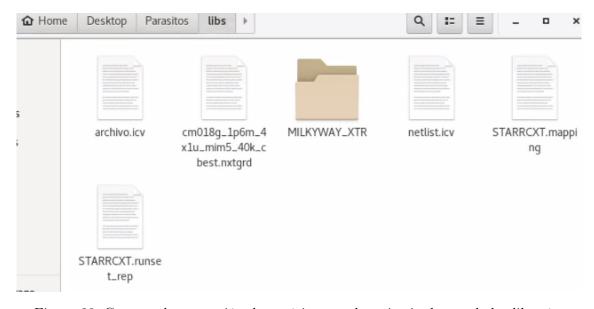

| 24.               | Dentro de la carpeta de parásitos dentro de libs                                | 53 |

| 25.               | Dentro de la carpeta de parásitos dentro de logs                                | 53 |

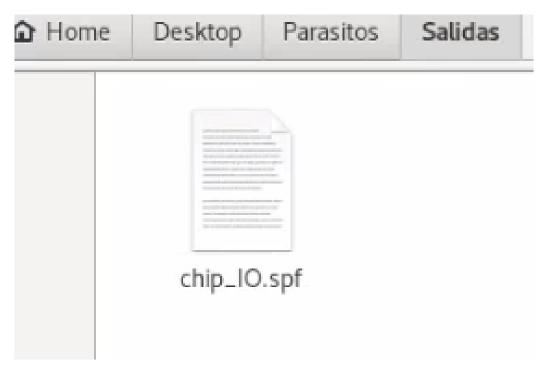

| 26.               | Dentro de la carpeta de parásitos dentro de salidas                             | 53 |

|                   | Dentito de la carpeta de parasitos dentito de sandas                            | 99 |

|                   |                                                                                 |    |

| 27.               | Carpeta de extracción de parásitos en el escritorio                             | 55 |

|                   |                                                                                 |    |

| 30          | Archivo de reporte | ا ماء | a extracción o | la narácitos |      |       |   |   |   |   |   |   |   |   |   | 6 |

|-------------|--------------------|-------|----------------|--------------|------|-------|---|---|---|---|---|---|---|---|---|---|

| <b>5</b> 0. | Archivo de reporte | ue 1  | a extraction c | ie parasitus | <br> | <br>• | • | • | • | • | • | • | • | • | • | U |

## Lista de cuadros

| 1.  | Código para realizar una simulación con VCS                             | 19 |

|-----|-------------------------------------------------------------------------|----|

| 2.  | Linea para creación de archivo con extensión .vcd                       | 20 |

|     |                                                                         |    |

| 3.  | Importación de librerías útiles en Python                               | 26 |

| 4.  | Lectura de un archivo                                                   | 26 |

| 5.  | Límite de lectura                                                       | 26 |

| 6.  | Listas utilizadas                                                       | 27 |

| 7.  | Búsqueda dentro del rango establecido                                   | 27 |

| 8.  | Búsqueda del número de bits que conforma la señal                       | 27 |

| 9.  | Búsqueda del número de bits que conforma la señal parte de salidas      | 28 |

| 10. | Búsqueda especial para encontrar caracteres                             | 28 |

| 11. | Filtro para la palabra que se buscó anteriormente en el cuadro anterior | 28 |

| 12. | Filtro del nombre módulo y almacenaje en una lista diferente            | 29 |

| 13. | Se crea el archivo final que se utilizará                               | 29 |

| 14. | Se escriben las variables dentro de la descripción del módulo nuevo     | 29 |

| 15. | Escritura dentro del archivo todas las entradas, salidas y los wires    | 30 |

| 16. | Línea para descripción de instancias                                    | 30 |

| 17. | Filtro para signos de puntuación                                        | 30 |

| 18. | Escritura de los pines de entrada y salida con librería de TSMC         | 31 |

| 19. | Escritura de pines de alimentación                                      | 32 |

|     |                                                                         |    |

| 20. | Código de inclusión de librerías utilizando la ruta de ubicación        | 36 |

| 21. | Restricciones de celdas de la biblioteca                                | 37 |

| 22. | Restricción de un bloque de la celda                                    | 37 |

| 23. | Lectura del archivo descrito en HDL                                     | 37 |

| 24. | Comandos de revisión de diseño                                          | 38 |

| 25. | Comando de compilación                                                  | 39 |

| 26. | Comandos de reportes                                                    | 39 |

| 27. | Escritura de archivos de salida                                         | 39 |

|     |                                                                         |    |

| 28. | Textos originales                                                       | 41 |

| 29. | Segunda parte de los textos originales                                  | 42 |

| 30. | Primer texto modificado                                                 | 42 |

| 31. | Segunda parte del primer texto modificado                        | 43 |

|-----|------------------------------------------------------------------|----|

| 32. | Continuación del primer texto modificado                         | 43 |

| 33. | Segundo texto modificado                                         | 44 |

| 34. | Continuación del segundo texto modificado                        | 44 |

| 35. | Contador original                                                | 45 |

| 36. | Contador modificado                                              | 46 |

| 37. | Tabla de verdad sin modificación                                 | 46 |

| 38. | Tabla de verdad con la modificación para la compuerta XOR        | 46 |

| 39. | Selector del texto original                                      | 47 |

| 40. | Selector del texto modificado                                    | 47 |

|     |                                                                  |    |

| 41. | Comando para montar un servidor compartido                       | 49 |

| 42. | Comandos extras para el servidor compartido                      | 51 |

|     |                                                                  |    |

| 43. | Script para ejecutar la verificación de extracción de parásitos  |    |

| 44. | Comandos e inclusión de librerías para completar la verificación | 59 |

Resumen

El proyecto se basa en la automatización de la etapa de síntesis lógica para llevar a cabo una etapa automática, rápida y efectiva del primer chip, diseñado y elaborado en Guatemala por estudiantes de la Universidad del Valle de Guatemala. Esta es la primera etapa para la realización del chip, es muy importante, ya que al ser la primera etapa los resultados deben de salir correctos para que no interrumpa el proceso de diseño. El objetivo por cumplir es verificar que los resultados obtenidos sean los adecuados después de realizar la automatización de dicho proceso y lograr obtener los archivos de Verilog que se utilizaran para realizar las pruebas en un FPGA Genesys Xilinx Virtex-5 LX50T para corroborar que el proceso de diseño del chip es exitoso.

La síntesis lógica es un código que describe un circuito en código Verilog para otorgar compuertas lógicas de hardware para una tecnología dada, la que se utilizaran en este diseño del primer chip será con librerías de TSMC. Este proceso de la etapa de síntesis lógica consta de dos pasos:

- Traducción implica comprender la descripción VHDL de las compuertas.

- Optimización que implica seleccionar la combinación más eficiente de las librerías de las bibliotecas de esa tecnología que se utiliza y las celdas para lograr relacionar las funciones y que este funcione de la manera más adecuada y que cumpla con su funcionalidad descrita.

En esta etapa se pueden agregar aspectos importantes para que el diseño de este funcione adecuadamente, como lo son las restricciones de diseño que se ven delimitadas por la tecnología que se utiliza, colocación de componentes de manera eficiente para optimizar de mejor manera el rendimiento del chip que se está desarrollando. Como resultados del proceso de esta etapa se pueden obtener 3 formatos de archivos, que son: '.sdc', este agrupa las netlist que el usuario configura durante el proceso de síntesis, el '.ddc' almacena toda la información de los netlist que se generaron al igual que las restricciones que se le asignan al circuito y el último '.v' es el archivo que contiene ya todas las netlist con las configuraciones

y restricciones que se hicieron previamente donde también se interconectan y se utiliza en las etapas siguientes para el seguimiento del desarrollo del chip.

Design Vision es una herramienta de software utilizada para llevar a cabo con éxito la etapa de síntesis lógica de un circuito que se describe a través de archivos HDL, este pasa por un proceso de síntesis donde se logra sintetizar para poder obtener archivos netlist a estructura de compuerta. Este puede utilizar librerías comunes y personalizadas como las que proporciona la empresa de TSMC.

VCS es una herramienta donde se realizan las verificaciones del diseño en el que se está trabajando, esta misma cuenta con un simulador y sistema para resolver limitaciones que pueda presentar el diseño. DVE, por otra parte, es un complemento de VCS, este permite simular y ver el comportamiento del diseño que se trabajó, con esto lograr ver que los resultados a la salida son los adecuados, gracias a la interfaz gráfica amigable es fácil de comprender y utilizar.

StarRC es una herramienta fundamental en la industria de EDA para la extracción de parásitos. Esta herramienta proporciona soluciones de extracción de silicio precisa y de alto rendimiento para SoC, digital personalizado y analógico / señal mixta. Esta implementación ofrece una facilidad de uso y productividad para poder acelerar el cierre de diseño y verificación de firma.

Abstract

The project is based on the automation of the logic synthesis stage to carry out a fast and effective automated stage of the first chip, designed and produced in Guatemala by students from the Universidad del Valle de Guatemala. This is the first stage for the realization of the chip, it is very important since being the first stage the results must be correct so that it does not interrupt the design process. The objective to be met is to verify that the results obtained are adequate after automating said process and obtaining the files of Verilog that are used to perform tests on a *Genesys Xilinx Virtex-5 LX50T* FPGA to verify that the chip design process is successful.

Logic synthesis is a code that describes a circuit in Verilog code to provide hardware logic gates for a given technology, which will be used in this first chip design with releases from TSMC. This process of the logical synthesis stage consists of two steps:

- Translation Involves understanding the VHDL description of the gates.

- Optimization that implies selecting the most efficient combination of the libraries of the libraries of that technology that is used and the cells to correlate the functions and that it works in the most appropriate way and that it complies with its described functionality..

At this stage, important aspects can be added so that the design works properly, such as the design restrictions that are delimited by the technology used, efficient component placement to better optimize the performance of the chip that is used. it is developing. As a result of the process of this stage, 3 file formats can be obtained, which are: '.sdc', this groups the netlist that the user configures during the synthesis process, the '.ddc' stores all the information of the netlists that were generated as well as the restrictions that are assigned to the circuit and the last '.v' is the file that already contains all the netlists with the

configurations and restrictions that were previously made where they are also interconnected and used in the following stages to follow the development of the chip.

Design Vision is a software tool used to successfully carry out the logical synthesis stage of a circuit that is described through HDL files, this goes through a synthesis process where it is possible to synthesize in order to obtain netlist files to structure of gate. It can use common and custom libraries such as those provided by the TSMC company.

VCS is a tool where the verifications of the design that is being worked on are carried out, it has a simulator and a system to resolve limitations that the design may present. DVE, on the other hand, is a VCS complement, it allows you to simulate and see the behavior of the design that was worked on, with this you can see that the output results are adequate, thanks to the friendly graphical interface it is easy to understand and use.

StarRC is a fundamental tool in the EDA industry for parasite extraction. This tool provides high-performance, precise silicon removal solutions for SoCs, custom digital, and analog/mixed-signal. This implementation offers ease of use and productivity in order to speed up design close and signature verification.

### CAPÍTULO 1

Introducción

Con la etapa de diseño de síntesis lógica y un flujo de diseño adecuado se hace la creación de un circuito en lenguaje HDL con el que es necesario contar antes de poder iniciar con la síntesis lógica, el cual toma uso de librerías de TSMC. Es necesario que este circuito final no presente ningún tipo de error para lograr avanzar a la siguiente etapa del flujo de diseño. Para el flujo se utilizó la herramienta de Design Vision, donde se colocan los comandos necesarios uno a uno, con lo que se demora en completar la síntesis lógica. Se emplea la terminal para facilitar de forma eficiente y correctamente en el menor tiempo posible, asegurando una síntesis lógica completa y adecuada y así entregar en un servidor compartido los archivos necesarios para uso en la siguiente etapa de flujo de diseño.

El presente trabajo esta organizado y dividido en 5 capítulos:

El capítulo 7 contiene una explicación del proceso que se quiere para poder analizar y realizar una lectura universal de un código descrito en HDL, para el cual se hizo uso de Python para realizar un script con el cual se hace una lectura y se reescribe en un archivo nuevo el módulo, las entradas y salidas del circuito que describe el funcionamiento. En este mismo capítulo se hace una explicación detallada de todo el código utilizado.

El capítulo 8 habla específicamente de las planificación de la automatización dividida en dos puntos importantes, el primero un script en bash para navegar dentro de directorios y tener una buena organización de carpetas ya que se eliminan los archivos y carpetas para evitar duplicidades; en el segundo script se tiene un archivo con todos los comandos necesarios que usa design vision para poder completar el proceso de síntesis lógica.

El capítulo 9 contiene todas las modificaciones importantes que se realizaron, estas me-

joras se hicieron al texto ya que se agrego mas al mismo y se hizo una cambio ya que el segundo texto es el primer texto solo que en idioma inglés. Al hacer este cambio se tuvo que hacer más grande el contador para que pueda pasar por todos los caracteres que se agregaron. El último cambio que se realizó fue la modificación de la tabla de verdad en la forma de seleccionar el texto, esto con el objetivo de poder generar una compuerta XOR para poder tener dos selectores.

El capitulo 10 se presenta toda la integración explicada a detalle de como se hizo un servidor compartido para entregar de una forma mas eficiente los archivos que se son necesarios para la siguiente etapa que es síntesis física.

El capítulo 11 se documenta todo el proceso para la automatización de la verificación de extracción de parásitos, en dicho capítulo se tiene la explicación de los archivos a utilizar así como los archivos que se generan y por último el orden de navegar entre directorios para tener una organización de carpetas, eliminar archivos de pruebas anteriores con el propósito de no tener archivos duplicados.

### capítulo 2

#### Antecedentes

El primer paso que se dio fue en 2014 cuando se logró tener un acuerdo con la empresa de Synopsys y de esta forma poder tener acceso al software para poder desarrollar tecnologías nuevas para Guatemala. Esta adquisición fue imperativa para que estudiantes se adentraran en esta rama de la electrónica que es la nanoelectrónica y que en ese mismo año se presente el primer estudiante en presentar un trabajo sobre VLSI por parte de UVG.

Synopsys Inc. es una empresa líder en desarrollo de software que se utiliza en el diseño de semiconductores, especializado en el campo de automatización de diseño electrónico. Estos productos ayudan a desarrollar y probar diseños de circuitos integrados antes de ser fabricados. Esto permite alcanzar un estándar óptimo en costos, tamaño y potencia. Ya con estas pruebas realizadas, Synopsys vende los productos finales a los fabricantes de semiconductores, informática, comunicaciones, electrónica comercial y agencias aeroespaciales.

En el año de 1970, el software de automatización del diseño electrónico se convirtió en un factor clave en los avances dramáticos de la industria electrónica. Cada vez más los circuitos integrados se hacían más complejos, junto a la escasez de ingenieros de circuitos integrados, crearon la necesidad de tener un software que pudiera reducir el tiempo de comercializar y costos de diseño, como también la confiabilidad de diseños de alta velocidad y de alta densidad.

Por la década de 1970 trajo la primera generación de EDA (Electronic Design Automation) y son:

- 1. Diseño asistido por computadora (CAD)

- 2. Ingeniería asistida por computadora (CAE)

#### 3. Automatización en el diseño electrónico (EDA)

La CAE logró un proceso en la automatización del diseño de los circuitos integrados más complejos, pero los ingenieros seguían invirtiendo mucho tiempo innecesario en conectar todos los nodos que se utilizan en los chips de silicio, con lo que la CAE no pudo seguir los rápidos cambios de la industria electrónica y la complejidad de los circuitos lo que llevo a la invención de un método mejor y es donde surgió la tecnología de EDA junto con Synopsys.

Aart de Geus, desarrolló una idea para una nueva tecnología de software llamada síntesis. Con esta síntesis los ingenieros podrían describir la funcionalidad de un circuito en lenguaje informático, en lugar de describirlos en términos de puertas individuales. Esta herramienta crearía automáticamente la síntesis lógica, esto les ahorra tiempo en diseño y libera a los ingenieros para soluciones de diseño para mayor eficiencia. La síntesis genera diseños de circuitos a partir de lenguajes que describen hardware como VHDL y Verilog, lo que permite esto es la nueva tecnología de EDA en la automatización del diseño del lenguaje de hardware.

Desde el 2019 se tuvo la visión de poder estudiar, diseñar y mandar a fabricar el primer procesador con una tecnología de 180 nm a la empresa de TSMC que es la empresa a nivel mundial que fabrica los procesadores, con lo que la universidad al igual que el trabajo arduo de estudiantes hicieron el proceso de la gestión para poder conseguir apoyo de parte de la empresa y así realizar el desarrollo del proyecto.

Los primeros avances realizados en el campo de la nanoelectrónica que se llevaron a cabo en la Universidad del Valle de Guatemala se dieron en el año 2013, donde se introdujo VLSI y en el 2014 se hizo un acuerdo con la empresa de Synpsys, donde se lograron obtener credenciales para obtener las herramientas necesarias para poder realizar el diseño y simulación de un nano chip. El primer trabajo de graduación realizado fue de parte del ingeniero en electrónica Jonathan de los Santos 2 donde se relaciona con las herramientas de VLSI y fue la base para el continuo desarrollo para los trabajos que se siguen realizando el día de hoy.

Seguido en el año 2020, los ingenieros electrónicos, Luis Abadia [3], Marvin Flores [4] y Matthias Sibrian [5] realizaron simulaciones del nano chip que se sigue diseñando actualmente con librerías de TSMC en los programas de IC Validator y IC Compiler I.