Diseño de circuito integrado con tecnología 180 nm usando librerías de diseño de TSMC: Ejecución de extracción de componentes parásitos y automatización del flujo de diseño

Joel Andrés González Herrera

# UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Diseño de circuito integrado con tecnología 180 nm usando librerías de diseño de TSMC: Ejecución de extracción de componentes parásitos y automatización del flujo de diseño

Trabajo de graduación presentado por Joel Andrés González Herrera para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala,

# UNIVERSIDAD DEL VALLE DE GUATEMALA Facultad de Ingeniería

Diseño de circuito integrado con tecnología 180 nm usando librerías de diseño de TSMC: Ejecución de extracción de componentes parásitos y automatización del flujo de diseño

Trabajo de graduación presentado por Joel Andrés González Herrera para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala,

Fecha de aprobación: Guatemala, 22 de junio de 2022.

Prefacio

Primeramente, quiero agradecerle a la Universidad del Valle de Guatemala que me ha estado dando una educación estelar durante estos años, siempre poniendo mi desarrollo como primera prioridad y dándome acceso a oportunidades, enseñanzas y seguridad durante mi tiempo de estudio. También se le agradece a la compañía de TSMC, cuyo trabajo, documentación y apoyo han sido inmensos para estas investigaciones y el avance tecnológico de Guatemala. Gracias a ambos, se tiene la oportunidad de realizar un proyecto que marca nuestras vidas.

Quiero agradecerle al ingeniero Jonathan de los Santos, quien apoyó este proyecto como asesor e hizo todo lo posible para cumplir este proyecto demandante con nosotros. Su esfuerzo y enseñanza nos iluminó como estudiantes en esta nueva frontera, permitiéndonos madurar como ingenieros, delvallerianos y como miembros de nuestro país. También agradezco a nuestro director de carrera, MSc. Carlos Esquit, cuyos esfuerzos para avanzar la educación en nuestro país y nuestra región nos han dado constantes oportunidades de aprendizaje.

Finalmente, agradezco a mi familia por su enorme apoyo a lo largo de mi vida. De ellos he aprendido las lecciones más cruciales, y espero con todo mi ser poder hacer bien con lo que ellos me han dado.

# Índice

| Pr  | refacio                     | ΙΙ |

|-----|-----------------------------|----|

| Lis | sta de figuras              | ΊI |

| Lis | sta de cuadros vi           | ΊΙ |

| Lis | sta de códigos              | IX |

| Re  | esumen                      | X  |

| Ał  | ostract                     | ΧI |

| 1.  | Introducción                | 1  |

| 2.  | Antecedentes                | 2  |

| 3.  | Justificación               | 4  |

| 4.  | Objetivos                   | 5  |

| 5.  | Alcance                     | 6  |

| 6.  |                             | 10 |

| 7.  | 7.1. Herramientas de diseño | 15 |

|    |          | 7.1.4. IC Validator                      | 16 |

|----|----------|------------------------------------------|----|

|    |          | 7.1.5. StarRC                            | 17 |

|    |          | 7.1.6. HSPICE                            | 18 |

|    |          | 7.1.7. Waveview                          | 18 |

|    | 7.2.     | Proceso de automatización                | 18 |

| 8. | Req      | uerimientos y uso de automatización      | 20 |

| 9. | Des      | arrollo de automatización                | 23 |

|    | 9.1.     | Síntesis lógica                          | 23 |

|    | 9.2.     | Síntesis física                          | 25 |

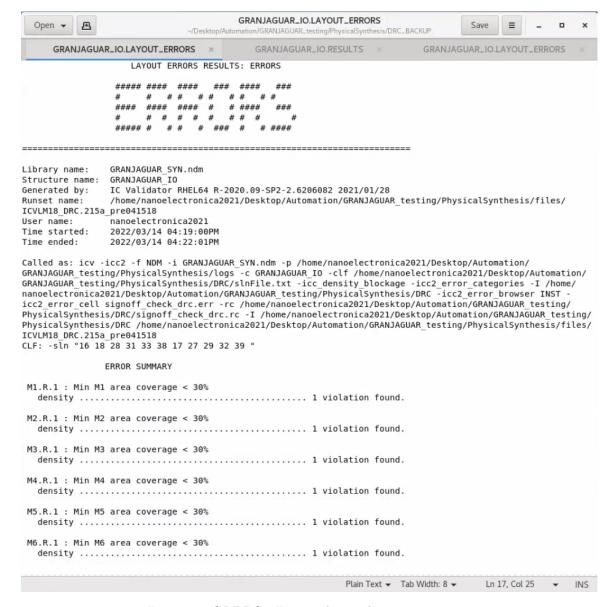

|    | 9.3.     | Design Rule Check                        | 29 |

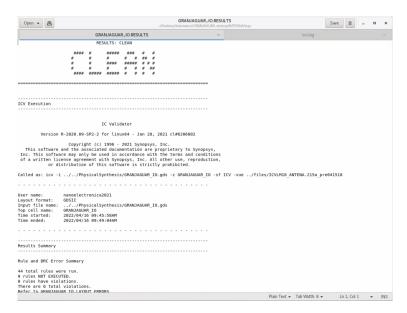

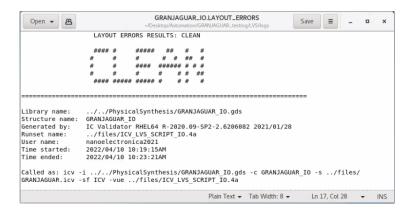

|    | 9.4.     | Layout versus Schematic                  | 30 |

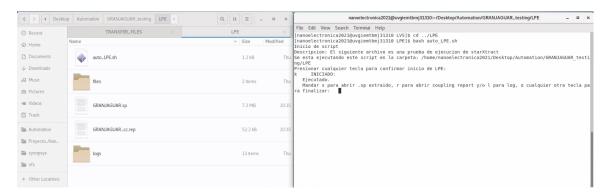

|    | 9.5.     | Layout Parasitic Extraction              | 33 |

| 10 | .Ext     | racción de ALU                           | 37 |

| 11 | .El C    | Gran Jaguar                              | 41 |

|    | 11.1.    | . Síntesis lógica del Gran Jaguar        | 42 |

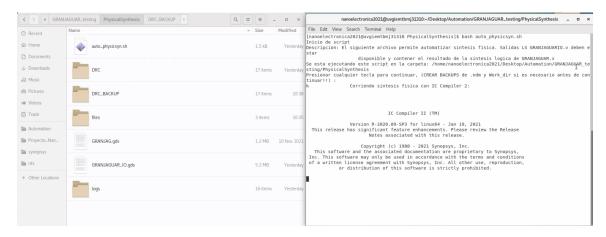

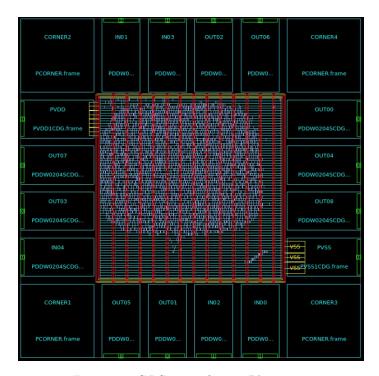

|    | 11.2.    | . Síntesis física del Gran Jaguar        | 44 |

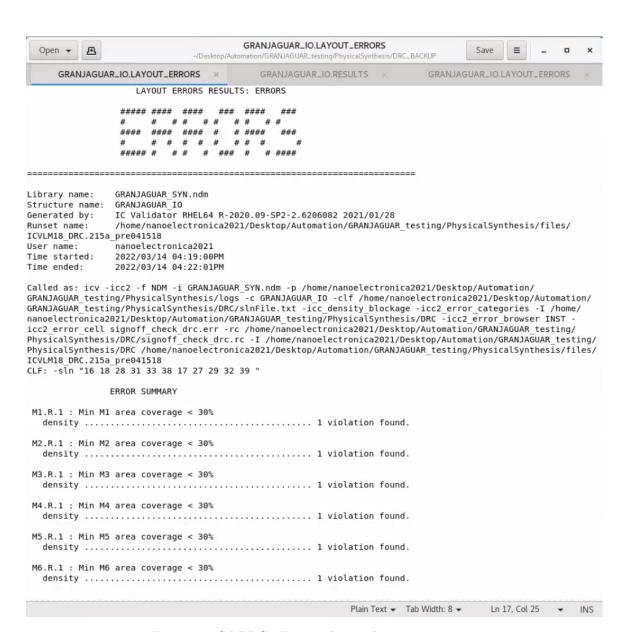

|    | 11.3.    | . DRC del Gran Jaguar                    | 47 |

|    | 11.4.    | . Verificación de antena del Gran Jaguar | 50 |

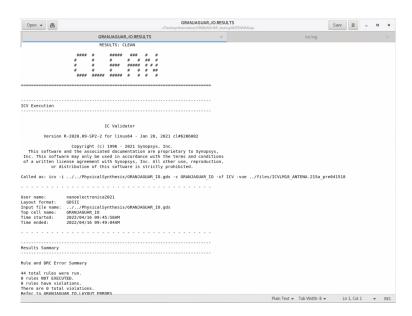

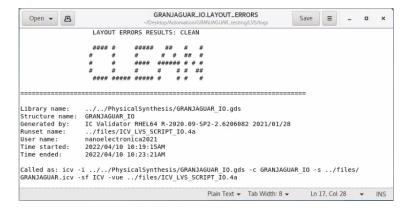

|    | 11.5.    | . LVS del Gran Jaguar                    | 51 |

|    | 11.6.    | . LPE del Gran Jaguar                    | 52 |

| 12 | .Con     | aclusiones                               | 54 |

| 13 | .  m Rec | omendaciones                             | 55 |

| 14 | .Bibl    | liografía                                | 56 |

| 15 | .Ane     | exos                                     | 59 |

|    | 15.1.    | . Flujo de diseño                        | 59 |

|    | 15.2.    | . Resultados                             | 61 |

|    | 15.3.    | . Scripts de automatización              | 65 |

|    | 15 /     | Dungata                                  | 79 |

# Lista de figuras

| 1.  | Diagrama de MOSFET [2]       | 9               |

|-----|------------------------------|-----------------|

| 2.  | Ley de Moore [4]             | 10              |

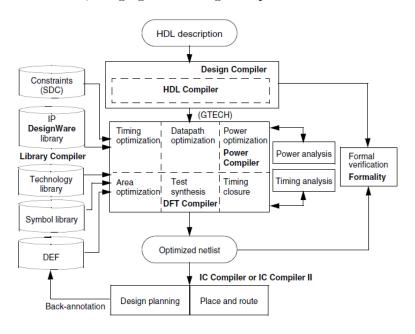

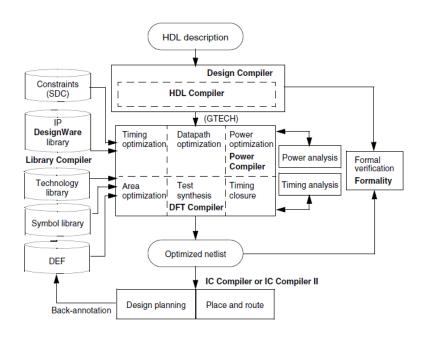

| 3.  | DC and ICC Flow [22]         | 25              |

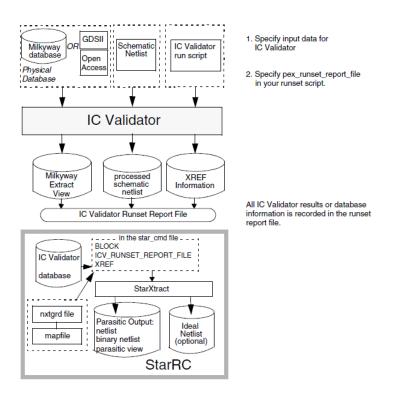

| 4.  | ICV and StarRC Flow [18]     |                 |

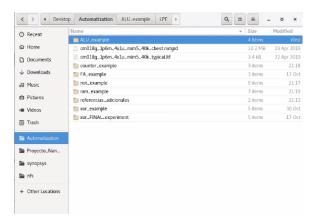

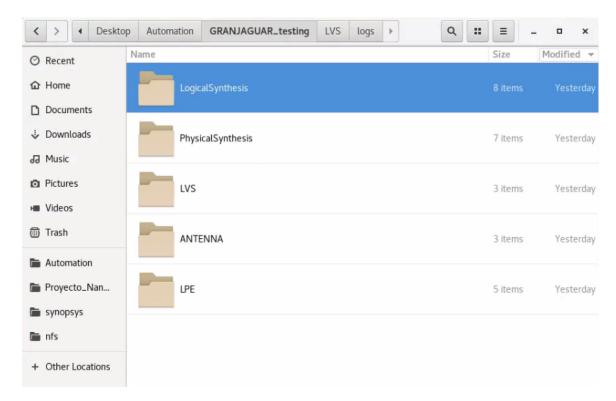

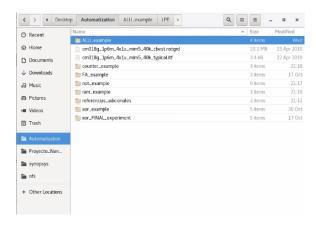

| 5.  | Fólder de automatización     | 37              |

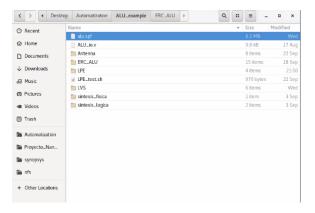

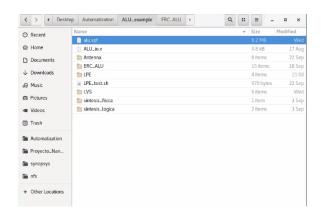

| 6.  | Fólder de ALU                |                 |

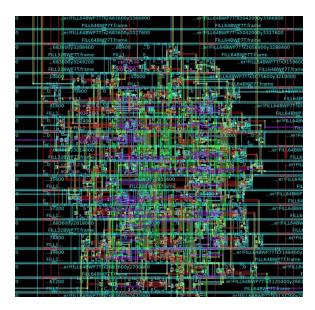

| 7.  |                              | 39              |

| 8.  | GJ Organización de procesos  | 42              |

| 9.  | GJ Entrada a síntesis lógica |                 |

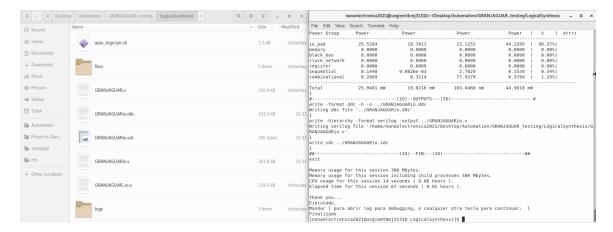

| 10. | Síntesis lógica en proceso   |                 |

| 11. | GJ Salida de síntesis lógica |                 |

| 12. |                              | 45              |

| 13. | 1                            | 45              |

| 14. |                              | 46              |

| 15. | 9                            | $\frac{-6}{46}$ |

| 16. |                              | 47              |

| 17. | GJ DRC - En proceso          |                 |

| 18. |                              | 48              |

| 19. |                              | 49              |

| 20. |                              | 50              |

| 21. | <u>.</u>                     | 51              |

| 22. | GJ LVS LAYOUT RESULTS        |                 |

| 23. |                              | 52              |

| 24. | *                            | 53              |

| 25. | DC and ICC Flow [22]         | 60              |

| 26. | ICV and StarRC Flow [18]     |                 |

| 27. | Fólder de automatización     |                 |

| 28. | Fólder de ALU                |                 |

| 29. | Zoom de layout ALU           |                 |

| 30. | GJ salida de síntesis lógica |                 |

| 31. | GJ DRC - Errores detectados para versión 2 | 63 |

|-----|--------------------------------------------|----|

| 32. | GJ verificación de antena                  | 64 |

| 33. | GJ LVS LAYOUT RESULTS                      | 64 |

| 34. | GJ LPE - Finalizado                        | 65 |

# Lista de cuadros

| 1. | Archivos de Design Vision para ejecución de síntesis lógica                      | 16 |

|----|----------------------------------------------------------------------------------|----|

| 2. | Archivos de ICC2 para ejecución de síntesis física                               | 16 |

| 3. | Archivos de $ICV$ para ejecución de procesos de verificación $\dots \dots \dots$ | 17 |

| 4. | Archivos de $StarRC$ para extracción de componentes parásitos                    | 18 |

| 5. | Organización de archivos para automatización                                     | 21 |

# Listings

| 8.1.  | Ejecución de scripts .sh desde el fólder que los contiene                                  | 20 |

|-------|--------------------------------------------------------------------------------------------|----|

| 8.2.  | Ejecución de scripts .sh desde un fólder superior                                          | 21 |

| 8.3.  | Reemplazo de nombres para archivos en mismo fólder                                         | 22 |

| 9.1.  | Automatización Design Compiler                                                             | 23 |

| 9.2.  | Síntesis lógica: Script de automatización (.script)                                        | 24 |

| 9.3.  | Automatización IC Compiler II                                                              | 25 |

| 9.4.  | Síntesis física: Primera parte de command file (.tcl)                                      | 26 |

| 9.5.  | Síntesis física: Segunda parte de command file (.tcl)                                      | 28 |

| 9.6.  | Síntesis física: Creación de .gds                                                          | 29 |

| 9.7.  | DRC: icv comando para openaccess                                                           | 29 |

| 9.8.  | DRC: icv comando para correr script                                                        | 29 |

| 9.9.  | DRC: Script de configuración y corrida                                                     | 30 |

| 9.10. | LVS: icv comando para openaccess                                                           | 31 |

| 9.11. | LVS primer paso: Traducción de Netlist                                                     | 32 |

| 9.12. | LVS segundo paso: Definición de headers                                                    | 32 |

| 9.13. | LVS tercer paso: Concatenación de headers                                                  | 32 |

| 9.14. | LVS cuarto paso: Traducción a CDL desde headers                                            | 32 |

|       |                                                                                            | 32 |

| 9.16. | LVS quinto paso: Creación de netlist.icv                                                   | 33 |

| 9.17. | LVS séptimo paso: Prueba de LVS                                                            | 33 |

| 9.18. | Automatizacion StarRC                                                                      | 33 |

| 9.19. | LPE script ejemplo para automatización (.cmd)                                              | 34 |

| 9.20. | Extracción de archivos .nxtgrd                                                             | 36 |

| 10.1. | LPE Result: ALU (parcial)                                                                  | 39 |

| 15.1. | autologicsyn.sh   Script para síntesis lógica                                              | 65 |

| 15.2. | autophysicsyn.sh   Script de síntesis física y DRC                                         | 67 |

| 15.3. | autoantenna.sh   Script para verificación de antena                                        | 68 |

| 15.4. | autoLVS.sh   Script para verificación LVS                                                  | 69 |

| 15.5. | autoLPE.sh   Script para extracción LPE                                                    | 70 |

| 15.6. | Síntesis lógica: .script para diseño principal                                             | 72 |

| 15.7. | Síntesis lógica: .script para diseño con entradas y salidas                                | 73 |

| 15.8. | Síntesis física: .tcl para diseño                                                          | 73 |

| 15.9. | LPE: .cmd con comandos utilizados para la extracción $\ \ldots \ \ldots \ \ldots \ \ldots$ | 76 |

|       |                                                                                            |    |

Resumen

El trabajo a continuación reporta sobre la investigación y el desarrollo del trabajo de graduación sobre la verificación y la automatización del flujo de diseño utilizado para el diseño del primer chip nanométrico de la región. Este documento sirve como reporte general de lo que fue desarrollado durante este periodo. Este imparte la metodología, decisiones, y ejecución de la verificación LPE y la automatización. Esta primera fase de verificación es posible por medio del proceso de extracción de componentes parásitos, resumido como LPE por sus siglas en inglés. Tomando referencias de los trabajos anteriores, junto con los recursos proveídos por *Synopsys*, se demuestra la aplicación y validez de la propuesta de un diseño propuesto. El segundo objetivo primario es de establecer y ejecutar por primera vez un método para automatizar dicho flujo de diseño con estas herramientas. El propósito siendo demostrar y probar este método, uno que simplifique el proceso y sea realizable por un solo usuario. El resultado final de este proceso son los archivos válidos y preparados de fabricación. En este trabajo se encuentra un reporte general del método que fue implementado para dichos objetivos.

Abstract

The following work reports on the research and development of the graduation project regarding the verification and automation of a design flow utilized to develop the first nanometric chip of the region. This document serves as a general report over what was developed during this period. It outlines the methodology, the decisions, and execution of the LPE verification and automation. The mentioned first phase of verification is possible through a Layout Parasitic Extraction, summarized as LPE. Taking references from previous works, along with the resources provided by *Synopsys*, the application and validity of the proposed design is shown. The second primary objective is to establish and execute for the first time a method for automating said design flow with these tools. The purpose being to demonstrate and prove the method for simplifying the process as much as possible for a user. The final result of this process are the verified and fabrication-ready files. In this work is a report over the method that was implemented for said objectives.

## capítulo 1

Introducción

La ciencia de chips electrónicos ha existido por un tiempo significativamente más corto al de otras ciencias. Esto se puede atribuir principalmente a su dependencia inicial de otras ciencias. Métodos y aplicaciones de química, ciencia y física fueron requeridos para iniciar la ciencia de la electrónica. Sin embargo, aún con la corta duración de avance que ha tenido esta tecnología, ha llevado a cambios vitales en todos los ámbitos. Desde las calculadoras que se han vuelto parte de las herramientas básicas en toda clase de investigación, a las computadoras más avanzadas que realizan las simulaciones complejas de estos mismos ámbitos. Claramente, toda la electrónica y, específicamente los chips, han llevado a grandes revoluciones en todos los campos de investigación imaginables.

En particular, la nanoelectrónica ha sido un área de evoluciones constantes. La famosa ley de Moore ha ejemplificado la velocidad de avances que se dan en esta ciencia, llevando a soluciones más y más sofisticadas para los problemas a pesar de ya proveer parámetros aceptables. Sin embargo, eso nunca ha sido suficiente. El deseo y el incentivo de mejores soluciones han llevado a este campo de ciencia a tener tantas evoluciones y revoluciones que se podría argumentar que ha tenido el mayor impacto en la vida diaria de la sociedad.

El resultado de este esfuerzo acumulativo de generaciones completas sirve como la parte central de los celulares, televisores, controles, e incluso en la computadora que fue utilizada para escribir este trabajo. Vive en la tecnología más común y más avanzada de estos tiempos.

Este es el contexto del campo al que se desea contribuir con todos los trabajos de investigación acompañando al presente documento. Guatemala como país se ha desarrollado al invertir en sus generaciones más jóvenes, aprendiendo las lecciones de países que están en una etapa avanzada, y adaptándose para tiempos nuevos. El propósito primario de estos esfuerzos siendo educativos, desarrollando las herramientas y métodos que serán dados en salones de esta universidad. Estos métodos serán dados a las generaciones después de la presente.

#### Antecedentes

Empezando en el año 2009, la facultad de ingeniería de la Universidad del Valle de Guatemala inicia esfuerzos para actualizar y expandir aprendizaje de tecnología nanométrica. Con la ocupación del MSc. Carlos Esquit en el puesto de director de la carrera de ingeniería electrónica, se expande los requisitos para dicha carrera. Para 2013, se da por primera vez el curso llamado Introducción al Diseño de Sistemas VLSI.

Durante el año 2019, se recibe la oportunidad de fabricar un circuito integrado en un chip con tecnología nanométrica. Esta oportunidad es gracias a Taiwan Semiconductor Manufacturing Company (de este punto en adelante llamado TSMC por sus iniciales). Este trabajo es continuación del trabajo realizado previamente por estudiantes de la Universidad del Valle.

El estudio para la definición del flujo de diseño se puede encontrar en el trabajo hecho por Steven H. Rubio. [13]

El primer paso de este flujo de diseño, específicamente la implementación de circuitos integrados desde lenguaje descriptivo fue visto el trabajo hecho por Luis A. Nájera. [11]

El uso de la herramienta VCS para la simulación fue detallado en el trabajo escrito por Jefferson N. Ruano. [12]

Adicionalmente, se vio la extracción de componentes parásitos en el trabajo escrito, en el mismo proyecto, por Charlie A. Cruz. [5]

Una verificación detallada de las reglas de diseños utilizadas en el proyecto fue hecha por Matthias Sibrian. [17]

Juan R. Girón realizó una verificación del diseño en silicio contrastado con el esquemático para este chip. [7]

También se realizó una corrección al anillo de entradas y salidas del chip y pruebas de antena para el flujo de diseño del chip. Esta fue completada por Marvin G. Flores. [6]

Finalmente, la línea de trabajo hecha con este propósito de utilizar estas herramientas para un flujo de diseño inicia con Jonathan de los Santos, quien durante el 2014 completó un sumador/restador de 32 bits con dichas herramientas. [15]

Como ha sido mencionado, este reporte se enfoca fuertemente en la automatización del flujo de diseño. Este es el primer trabajo con este enfoque, basándose en el esfuerzo hecho por todas las personas arriba y referidas que han desarrollado estos trabajos.

Justificación

El trabajo para hacer un chip a estas escalas no es simple. Proporcional a la sofisticación necesaria en los chips, existe un proceso igualmente detallado para encontrar, filtrar o minimizar todo tipo de errores en la implementación, diseño, construcción, fabricación y aplicación de los circuitos finales. Esto incluye también los requisitos del proceso de fabricación, que existen fuera del alcance de este trabajo. Por ejemplo, estos incluyen las condiciones de limpieza necesarios para asegurar el funcionamiento de la solución propuesta.

Como sería evidente, este proceso de fabricación solamente existe después del proceso de diseño. Este se dedica a la implementación de los métodos desarrollados y resulta en un diseño de circuito que cumple todos los requisitos del problema, todas las reglas de diseño, todas las regulaciones requeridas, incluso con sobre-protecciones para asegurar que el proceso completo no sea en vano. Un ejemplo simple de esto es el requisito de distancia entre vías, o en otras palabras, entre conductores. Sin esta clase de regulación, el circuito fácilmente se podría encontrar con un cortocircuito que resulta en una falla completa del circuito.

En este trabajo se prioriza la vista de verificación y automatización del proceso de diseño. Estas dos son partes extremadamente importantes para el desarrollo de las aplicaciones de estas herramientas. La verificación por medio de la extracción de parásitos se presenta como una vista global del comportamiento del circuito. En especial, se establece que capacitancias, resistencias e inductancias parásitas que resultarían por medio del diseño presente de un layout, y que estas no hayan drásticamente alterado o anulado el comportamiento deseado del sistema físico. Estas simulaciones finales podrán validar el diseño como tal, dejando ninguna duda que el layout se comportaría en la realidad como fue planificado.

Segundo, se ve la automatización del proceso general del flujo de diseño. Para esto, se requiere una revisión del sistema completo y de cada fase de diseño, con apoyo y comunicación con los demás grupos de trabajo a fin de establecer el procedimiento de las secciones más específicas del proceso. Estas herramientas, dadas como secciones de cada fase, podrán facilitar el estudio de esta tecnología, estableciendo una ruta más directa con propósitos tanto educativos como de industriales.

Objetivos

#### 4.1 Objetivo general

Realizar el proceso de extracción de parásitos en el *Layout* final del chip diseñado y junto con todos los grupos de trabajo con una comunicación constante y efectiva, automatizar el flujo de diseño de tecnología nanométrica mediante scripts, facilitando la elaboración de trabajos futuros.

#### 4.2 Objetivos específicos

- Ejecutar el proceso de extracción de parásitos sobre el *layout* final del chip diseñado, proveído por el último grupo de trabajo de síntesis física.

- Entablar un método para la producción de archivos para simulación en HSPICE cuando se esté trabajando con librerías originales. Este método permitirá verificar el funcionamiento del sistema resultante de los circuitos al extraer los componentes parásitos.

- Explorar las herramientas de diseño con Synopsys para la creación de scripts de comandos que sirvan para el avance del proceso, tanto para facilitar casos generales como casos particulares, facilitando debugging y sus verificaciones.

- Facilitar el proceso en cada fase de flujo de diseño, de tal manera que se pueda apoyar al resto del grupo en su diseño.

- Automatizar de manera independiente cada fase del flujo de diseño, permitiendo la revisión de errores para generalizar cada caso de diseño.

- Integrar todas las fases del flujo de diseño para desarrollar un Design Flow automatizado.

Alcance

Debido a la naturaleza de este trabajo y el hecho que este fue hecho en conjunto, este reporte se dedica principalmente a explicar el proceso de automatización y ve la extracción de parásitos del chip propuesto. El funcionamiento detallado de cada proceso interno al diseño de flujo se encuentra en los reportes respectivos de los trabajos que acompañan a este.

En orden de su posición en el flujo de diseño: El proceso de síntesis lógica encuentra en el trabajo de Elmer Torres. La síntesis física con su verificación en DRC y reglas de antena se encuentra en los trabajos de Antonio Altuna, Julio Shin, y José Ayala. La comparación de los diseños de Layout contra el esquemático (LVS) fue visto por José Ruiz. Finalmente, la verificación de síntesis lógica al igual que la verificación final de extracción de parásitos se encuentra en la investigación en proceso por Gerardo Cardoza.

Este trabajo se limitará a explicar la sección de este proyecto que está fuera del alcance de dichos trabajos, por lo que sería recomendable tener estos trabajos a mano para complementar cualquier modificación. Con eso dicho, este reporte puede operar como una introducción o reporte general de todo el proceso de diseño. En otras palabras, en este reporte se encuentra una descripción de todo lo que fue completado durante este proyecto con el propósito de automatizar el trabajo que se realizó anteriormente. Este reporte, complementado por el trabajo especifico hecho por cada uno de los compañeros mencionados, darán una vista detallada de lo que fue trabajado por los estudiantes de ingeniería electrónica involucrados en este proyecto.

Sin embargo, este reporte no estaría completo sin describir lo que hace cada proceso en el flujo de diseño. Por lo que este trabajo se dedicará a dar una descripción completa de lo que se pretende realizar en cada proceso, dando el método de automatización y las opciones utilizadas para cada proceso mencionado. Por lo tanto, en este trabajo, se pretende replicar los procesos hechos por los compañeros, y no se mejoran. Las recomendaciones de cada compañero de trabajo fueron tomadas en cuenta, pero la mejora de los mismos se dejan al siguiente grupo de trabajo. Por medio de todos los reportes hechos, será posible darles un panorama completo del proyecto.

Como parte del flujo a ser completado, también se detalla el proceso de Layout Parasitic Extraction (LPE), junto con los problemas encontrados y sus soluciones propuestas. Esta sección se puede considerar una continuación del trabajo hecho el año anterior por Charlie Cruz. Este trabajo también propone soluciones a los problemas principales encontrados por nuestro compañero Cruz.

Y finalmente, se detallará el proceso de automatización llevado por el equipo. Esto servirá con el motivo principal de facilitar futuras pruebas, habiendo hecho la implementación y con este trabajo conteniendo explicaciones de como se implementó cada sección.

## CAPÍTULO 6

Marco teórico

El diseño de un chip nanométrico requiere investigación y dominio de varias herramientas para ejecutar correctamente el flujo de diseño. Y estas herramientas requieren dominio en sus respectivas áreas y detalles para poder explicar sus objetivos y lo que realizan en este proyecto. Existen múltiples temas que se deben investigar para poder analizar esta tecnología. Entre ellos, se incluyen los transistores MOSFET, VLSI, y fabricación. Es necesario tener el mismo entendido de los temas que forman la base de este proyecto y de los proyectos que lo complementan.

#### 6.1. MOSFETs

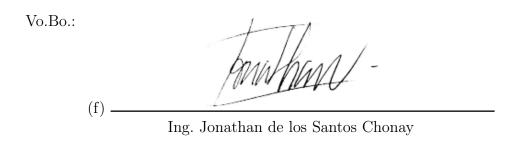

La construcción de nanochips y las compuertas lógicas que se han visto es principalmente gracias a los *MOSFETS*. Su construcción es parecida a los transistores *JETS*. Se utiliza el campo generado por un voltaje en la terminal de *gate* que crea un canal conductivo en el cual pueden fluir los electrones de *source* a *drain*. Estos, acumulados y en conjunto, crean una red de señales lógicas que realizan el procesamiento necesario para chips.

Figura 1: Diagrama de MOSFET [2]

Esta tecnología diminuta es la sección fundamental que permite la lógica necesaria, como el elemento más fundamental, este representa la vista más detallada de la tecnología en estos chips. Esta revolución en tecnología permite el procesamiento a gran escala que se ve en el resto de los chips. Este elemento, por medio de la fabricación que se detalla a continuación, puede ser construido en waffers y con una suficiente exactitud, resultan en los dispositivos poderosos y diminutos que se ven hoy en día. [2]

### 6.2. Very Large-scale Integration (VLSI)

VLSI se define simplemente como la creación de un circuito integrado en un chip, utilizando compuertas CMOS. Primeramente descrito con MOSFETs en Fairchild Electronics por Frank Wanlass y Chi-Tang Sah en 1963, estas compuertas lógicas fueron llamadas CMOS. Estas forman la base de los electrónicos de hoy. Esto es debido al costo reducido de producción y el menor consumo de energía dado por esta tecnología. [10]

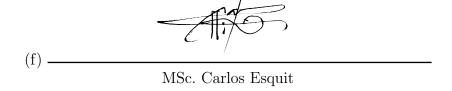

Esta velocidad del avance tecnológico ha acelerado por décadas. Gordon Moore es famoso y reconocido el día de hoy, no solo por fundar Intel, sino por la observación de *Moore 's Law* que dice que *el número de transistores en un circuito integrado se duplica cada dos años*. La exactitud de dicha predicción considera valiosa. Sin embargo, esta exactitud es secundaria a la observación del aceleramiento que habría en la tecnología mientras fuera avanzando.[4]

Figura 2: Ley de Moore [4]

Diseño VLSI a apoyado este crecimiento. En la misma área en la que se ingresaban miles de transistores MOS, se ha desarrollado para poder ingresar decenas de miles, millones, decenas de millones. Actualmente, se ha alcanzado 1 000 millones de transistores MOS en un solo circuito integrado. [10].

#### 6.3. Flujo de diseño

El siguiente tema con relevancia es el flujo de diseño. Este flujo se refiere al proceso de diseño e implementación que ha sido estandarizado para esta clase de tecnología. Esta estandarización está hecha para filtrar todo tipo de errores, tanto de aplicación, de lógica, de corto, de falsos contactos, de ruteo, y cualquier otro tipo de error relevante. Este proceso incluso toma en cuenta la posibilidad de error en la fabricación. Esto se debe a que existen varias reglas de diseño que pueden ser consideradas sobre-restringidas. Esto tiene una razón. Estas pretenden garantizar que la solución final operará correctamente dentro el margen de error que puede existir en la fabricación.

Este proceso de diseño se puede dividir en dos partes: Fase *Front-end*, que se refiere a la síntesis lógica y a nivel de aplicación. La segunda parte se le llama *Back-end*, que ve el funcionamiento estructural del sistema. [10]

#### 6.3.1. Front-end Design

Una definición útil de la primera mitad del flujo de diseño puede considerar que esta se encarga del *método* o más bien la solución general del sistema. Este principalmente define el comportamiento del sistema, con el diseño específico y físico perteneciendo a la siguiente sección. Estas incluyen:

#### 1. Diseño lógico

Esta es la sección principal de esta mitad del flujo de diseño y es la más dependiente de asistencia de un diseñador. El propósito de un diseño es de resolver un problema.

Debido a esto, dicho diseño depende principalmente de una descripción del comportamiento del sistema propuesto. El resultado de este proceso va a ser un archivo o una serie de archivos .v o Verilog que describan el sistema a ser implementado. Este resultado debe cumplir con las especificaciones del problema y requiere ser verificado apropiadamente.[10]

#### 2. Síntesis lógica

Similar al diseño lógico, esta sección tiene como objetivo tomar el comportamiento de la sección anterior y llevarlos a una descripción estructural. Verilog tiene una facilidad de programación, en la que circuitos se pueden describir de manera que solamente describen comportamiento. Esto tiene su utilidad, pero esto no es utilizado directamente para el proceso de fabricación. Se requiere una definición exacta del sistema o más bien una solución detallada. En eso entra la síntesis lógica, que finaliza la implementación del diseño original. Existen herramientas que facilitan esta transición y tienen como salida un archivo verilog que realmente describen la solución propuesta, con base en una librería importada. Esta que no se limita a comportamiento, sino que detalla a los componentes que serán utilizados en este proceso. [9]

#### 3. Netlist de compuertas

Esta es una sección de vital importancia. La descripción de cualquier circuito Verilog no va a ser suficiente para empezar el proceso de *floor planning*. Para empezar, no se tienen los datos de como es cada compuerta lógica necesaria. Para esto se utiliza una librería. Las herramientas disponibles con Synopsys son capaces de llevar el archivo Verilog a un netlist que conecte el comportamiento con las librerías. En este caso, se utilizarían las librerías TSMC. Estas podrían ser ligadas directamente con layouts respectivos que cumplen los requisitos necesarios en el diseño. [11]

#### 4. Verificaciones

Esta sección, en lugar de ser la parte 4 del flujo de diseño, sería más útil considerarlo como una sección paralela al proceso. Estas verificaciones son un proceso iterativo, donde se realiza constantemente verificaciones de las partes anteriores. Existen tres principales verificaciones a realizar durante esta mitad del flujo.[7]

La primera de estas es la verificación de funcionalidad, que podría considerarse extensión o prueba del Diseño Lógico. La segunda verificación relevante es la revisión de la síntesis lógica. Finalmente, la última verificación examina las *netlists* como resultados. Estas son partes vitales, operando como correcciones o *feedbacks* del sistema para corregir problemas del diseño desde estos pasos. Para sistemas complejos, es casi garantizado que habrá algún error que deba ser corregido antes de avanzar a los próximos pasos.

#### 6.3.2. Back-end Design

Para la segunda mitad de este flujo de diseño, se ve el paso después del método de solución. Es decir, una solución detallada del circuito. En la sección anterior solamente se obtiene una idea general del resultado final. En cambio, en esta mitad, el resultado es el diseño completo de un layout que cumple los requisitos del problema, en otras palabras, el resultado es

un layout preparado para fabricación. Varios pasos de esta sección son simplemente pruebas o *checks* que sirven para asegurar que el layout pueda funcionar correctamente después de ser implementado.

#### 1. Síntesis física

A partir del esquemático original, se debe producir el layout, que sirve como una descripción de como serán colocados cada uno de los elementos necesarios para el circuito. En el caso de nanoelectrónica, este es un chip considerablemente pequeño, y por lo tanto, la fabricación debe ser precisa. Sin un trabajo preciso, sería imposible implementar esta clase de tecnología sin que un error fatal invalide la solución y por lo tanto, invalide el trabajo invertido en el mismo.

#### 2. Routing

Ruteo se refiere al proceso de crear los caminos conductivos necesarios para que se conecten los elementos como fueron propuestos en el esquemático. Parte de este proceso puede ser automatizado, utilizando la herramienta de auto-ruteo. Sin embargo, esta puede fallar en casos más complejos. Por lo que siempre se depende de un usuario que se asegure que se cumpla todas las reglas, y todos los caminos para hacerlo semejante a la solución propuesta en el esquemático. Las siguientes son pruebas utilizadas para encontrar problemas que no cumple el layout con el objetivo de arreglar las discrepancias y los detalles que podrían llevar a un error fatal del diseño.

#### 3. Design Rule Check

Como su nombre indica, DRC se refiere a la parte del proceso de diseño que cumple las reglas de diseño. Como fue mencionado, estas reglas son regulaciones necesarias, en ocasiones son sobre-protecciones que no siempre son vitales. Sin embargo, estas llegan a ser importantes en casos particulares y se debe diseñar tomando encuenta posibles errores en alimentación, voltajes, fabricación, capacitancias o cualquier otro cortocircuito que debe ser eliminado para que se cumpla lo que se busca.

#### 4. Layout versus Schematic

También llamado LVS, el propósito de este prueba es una comparación. El objetivo es encontrar toda diferencia existente entre una solución propuesta en el esquemático y diseño resultante. Esta comparación y su validez es vital para las siguientes secciones. Aunque un diseño de layout haya sido validado por la prueba DRC, eso no garantiza que sí es representativo del esquemático propuesto. Es precisamente en esta sección donde se valida la exactitud de layouts para representar la solución propuesta en la primera sección.

#### 5. Layout Parasitic Extraction

Como una de las últimas verificaciones, existe LPE. Una vez ya se valida el diseño con LVS y DRC, demostrando que se está hablando del mismo circuito funcional en ambos casos, se debe correr un proceso que transfiere el circuito de *layout* a un formato en el que puede ser simulado. Para esto, se utiliza *StarRC* para la generación y *HSPICE* para la simulación. Desde este punto, se puede simular un circuito exacto que corresponde al diseño final del plan de piso. Es por medio de esto que se podría hacer una verificación tanto visual, especialmente de comportamiento y función. Sin

esta sección, se toma el riesgo que existan capacitancias parásitas o algún elemento agregado que atrase o incluso invalide el comportamiento pedido del diseño.

Metodología

Debido a la dicha complejidad de diseño que será inevitable en esta clase de tecnología, es importante desarrollar un librería clara de estrategias, recursos y herramientas que puedan ser utilizadas durante este proceso. Se ha descrito a detalle el flujo de diseño general utilizado para esta clase de aplicación. Es lógico asumir que existen compañías como *Synopsys* que han desarrollado herramientas para seguir este proceso de manera efectiva. Estas son descritas a continuación.

#### 7.1. Herramientas de diseño

Desde cero, sería difícil diseñar un chip de una calidad satisfactoria. Esta limitación no se da solamente por las dificultades de fabricación, sino por los archivos y programas necesarios para poder ejecutar estas operaciones complejas.

Para lograr esto se basará en los servicios y programas proveídos por *Synopsys*. Dicha compañía se especializa en automatización de diseño de chips electrónicos con una gran número de aplicaciones. Especialmente desde el año 2014 a la actualidad, ha expandido sus servicios. Esta base es importante para avanzar en las áreas relevantes. Estos servicios y productos son la base de este proyecto. [25]

Los distintos servicios o herramientas tienen objetivos distintos. Algunos tienen operaciones similares. A continuación se encuentra una lista de los programas utilizados durante este trabajo:

#### 7.1.1. Custom Compiler

CC es descrito como 'el corazón de la plataforma Synopsys de Diseño'. Este servicio es una herramienta de diseño completo de circuitos integrados. Por medio de diversas interfaces gráficas, este producto permite una implementación manual de cada parte del proceso necesario. Tanto como herramienta educativa y como implementación profesional, tiene una gran utilidad en su simplicidad para facilitar las soluciones más complejas que se desean implementar. Este visualiza y ejecuta cada parte del proceso necesario para un diseño exitoso. [21]

Desde el inicio de este proyecto, y específicamente desde la integración de nanotecnología al currículo de la Universidad del Valle, *Custom Compiler* es la primera herramienta que nuevos estudiantes llegan a utilizar. Este funciona como un *hub* o una centralización de los servicios a continuación. Por medio de este, que hace las llamadas apropiadas a los programas individuales, permite que un usuario familiarizado con sus funciones pueda ejecutar cada sección del flujo de diseño de manera manual.

#### 7.1.2. Design Vision

Síntesis lógica, como fue mencionado anteriormente, debe realizar una transición de una programación de verilog a un programa que describe este circuito original en base de los componentes de librería que puedan ser utilizados en la síntesis física. En esta primera fase, es necesario tener una herramienta que pueda analizar una propuesta codificada en Verilog y encontrar elementos equivalentes en la librería de uso que pueda ser implementado en un Layout. Esta es una parte esencial de la automatización, debido a que el procedimiento sería ineficiente si fuera necesario buscar manualmente cada una de estas equivalencias. Otra opción, que sería incluso menos eficiente, necesitaría la construcción de cada elemento, cada gate, y cada layout de manera manual cada vez. Debido a que esto claramente no sería realizable para la mayoría de casos, Se presenta la necesidad de una herramienta que procese la síntesis lógica para informar a las siguientes secciones del plan de diseño con los elementos necesarios. Esta es la función de Design Vision.[8]

Durante este proyecto, gracias al trabajo de Elmer Torres, se pudo obtener un método directamente de DV que permite realizar la síntesis lógica desde una interfaz gráfica. [26] Se pretende generalizar este método para poderlo completar solamente con comandos, desde una terminal.

Con el motivo de mejor explicar el procedimiento, en la siguiente página se encuentra el Cuadro 1. Este es un desglose de los archivos principales del proceso. Este no incluye archivos de referencias generales como librerías en este proceso. Tampoco incluye archivos de registro o *logs* que se abren en el transcurso del programa.

Por supuesto, debido a la necesidad de agregarle puertos de entrada y salidas, esto quiere decir que este proceso debe correrse dos veces. Una vez para realizar la transición del circuito principal, y la segunda para tomar la salida de esta primera corrida, y agregarle los puertos de entradas y salidas.

Cuadro 1: Archivos de Design Vision para ejecución de síntesis lógica

| Nombre y extensión | Uso     | Descripción                                                                                  |

|--------------------|---------|----------------------------------------------------------------------------------------------|

| Verilog (.v)       | Entrada | Archivo describiendo el circuito de entrada para síntesis lógica.                            |

| DVLogSyn (.script) | Script  | Script describiendo instrucciones a correr incluyendo la importación de entradas.            |

| Verilog final (.v) | Salida  | Archivo describiendo el circuito de entrada ya puesto en términos de la librería solicitada. |

#### 7.1.3. IC Compiler

ICC I y II son conocidos como soluciones de place-and-route. Se han presentado como la mejor solución y herramienta con calidad de resultados. Facilitan el plan de diseño, exploración de diseño inicial, junto con optimización y velocidad de ruteo. Este nivel de análisis es necesario para la complejidad de circuitos que son requeridos de esta aplicación. [23]

Esta herramienta fue utilizada por el equipo de síntesis física de Altuna, Shin, y Ayala. Por las siglas de sus nombres, este equipo usualmente firma sus trabajos con **ASA**. Según su trabajo, se avanzó y optimizó el trabajo de síntesis física. [3] [16] [1]

A continuación, se listan archivos relevantes en la ejecución de este proceso, esto no incluye archivos de registro o *logs* que se abren en el transcurso del programa:

Cuadro 2: Archivos de ICC2 para ejecución de síntesis física

| Nombre y extensión  | Uso     | Descripción                                                                                  |

|---------------------|---------|----------------------------------------------------------------------------------------------|

| Verilog final (.v)  | Entrada | Archivo describiendo el circuito de entrada ya puesto en términos de la librería solicitada. |

| Libreria_Syn (n/a)  | fólder  | Folder conteniendo información del proceso y compuertas.                                     |

| ICC2PS (.tcl)       | Script  | Script describiendo instrucciones a correr para síntesis física.                             |

| $Nombre\_IO~(.gds)$ | Salida  | Extracción de archivo describiendo circuito sintetizado.                                     |

#### 7.1.4. IC Validator

Esta herramienta tiene como función principal validar diseños. Esto sería imposible por medio de un método manual debido a las reglas detalladas que son requeridas en DRC y LVS. Para esto, se requiere un programa o servicio que centralice estas verificaciones y provea apoyo en ubicar errores, proponer soluciones y al mismo tiempo mantener una eficiencia y

capacidad de ser escalado apropiadamente con la complejidad del problema a resolver. Este es el rol de ICV en el flujo de diseño. [24]

ICV, por supuesto, es de gran utilidad para las tres grandes pruebas necesarias durante el proceso de Backend de diseño. Estas pruebas incluyen: DRC, Verificación de reglas de Antena y LVS. [3] [14]

A continuación, se listan archivos relevantes en la ejecución de estas verificaciones, esto no incluye archivos de registro o *logs* que se crean en el transcurso del programa:

Cuadro 3: Archivos de ICV para ejecución de procesos de verificación

| Nombre y extensión               | Uso           | Descripción                                                                                          |

|----------------------------------|---------------|------------------------------------------------------------------------------------------------------|

| ICVLM18_LM16 (.4a)               | Configuración | Archivo con reglas DRC y Antena para<br>la configuración del usuario.<br>Propiedad de TSMC.          |

| LVS_RC (.4a)                     | Configuración | Archivo con opciones del proceso<br>LVS, incluyendo la generación de archivos.<br>Propiedad de TSMC. |

| (.LAYOUT_ERRORS)                 | Salida        | Archivo describiendo las fallas de reglas que fueron encontrados para LVS.                           |

| (.RESULTS)                       | Salida        | Archivo describiendo las fallas de reglas que fueron encontrados para DRC.                           |

| STARCXT (.mapping y .runset_rep) | Salida        | Archivos de salida de LVS, utilizados en extracción de parásitos.                                    |

#### 7.1.5. StarRC

Esta herramienta se enfoca principalmente en la extracción de parásitos. Como fue mencionado, dicha prueba es un proceso que transfiere el layout como fue diseñado y lo implementa como un archivo describiendo el circuito para ser simulado. Esta verificación es importante porque se necesitan considerar las capacitancias parásitas, irregularidades, entre otras imperfecciones que surgen en el layout. StarRC es capaz de ejecutar este paso, procesando el diseño actual a una versión que pueda ser simulada con parámetros idénticos a los elementos reales. En dicha sección se verán imperfecciones y será posible considerar cambios relevantes para el diseño. [20]

El proceso ejecutado por medio de este programa es extracción de parásitos de layout, o *LPE* por sus siglas en inglés. Este era originalmente ejecutado por medio de *CC*. [5] Después de dificultades abriendo su interfaz gráfica, se pasó a realizarlo por medio de comandos y un archivo .cmd. Este proceso es detallado en su sección. A continuación, se listan los archivos utilizados por este sistema:

Cuadro 4: Archivos de StarRC para extracción de componentes parásitos

| Nombre y extensión               | Uso     | Descripción                                                                             |

|----------------------------------|---------|-----------------------------------------------------------------------------------------|

| STARCXT (.mapping y .runset_rep) | Entrada | Archivos de salida de LVS, utilizados en extracción de parásitos.                       |

| $LPE\_TSMC\_script~(.cmd)$       | Script  | Archivo detallando opciones de extracción incluyendo direcciones a Archivos de entrada. |

| $CIRCUITO\_cc\ (.rep)$           | Salida  | Archivo de reporte de Coupling                                                          |

| CIRCUITO (.sp)                   | Salida  | Archivo descriptivo de circuito                                                         |

#### 7.1.6. HSPICE

Como herramienta adicional que es particularmente útil para la sección de verificación, existe la herramienta de *HSPICE* que también le pertenece a *Synopsys*. Este es un simulador de circuitos. Este es una de las herramientas principales para estos diseños, ya que por medio de este simulador, es posible realizar numerosas pruebas de manera precisa de todo tipo de circuito válido. Una de estas es la simulación en estado transitorio, que permitirá observar el comportamiento de un sistema una vez recibe instrucciones específicas. [5]

#### 7.1.7. Waveview

Como complemento a HSPICE, existe WV. Esta es una herramienta de visualización que puede observar los resultados de HSPICE. Sin esta clase de herramienta, la verificación de comportamiento dependería principalmente de análisis numérico de los resultados dados de una simulación. Por medio de WV es posible realizar una verificación visual del comportamiento. [19]

#### 7.2. Proceso de automatización

El método general propuesto para automatizar el proceso de diseño consistirá en numerosos scripts .sh en Linux, específicamente CentOS. Estos se dedican a llamar a los programas debidos, abriéndolos e ingresando instrucciones en el formato de documentos llamados runsets. El inicio de este proceso debe iniciar con archivos Verilog, ingresados por el usuario, o importados de algún ejemplo. Los runsets adecuados, especialmente en sus secciones donde se apuntan a los archivos de entrada y salida podrán ser modificados de manera manual o utilizando una herramienta de sustitución para la adaptación a un circuito nuevo. Este programa deberá crear, copiar, y/o modificar los scripts utilizados para el proceso. Desde este punto, el objetivo es llegar a obtener los archivos finales de fabricación. Esto es posible debido a la función de comandos que llaman a las herramientas apropiadas. El detalle de cada herramienta, como funciona y los detalles están más allá del alcance de este proyecto.

Sin embargo, es importante estudiar sus limitaciones y como podrá adaptarse el sistema para completarlo.

Por supuesto, no se puede asumir que el proceso es exitoso todo el tiempo. Para adaptarse a esto, se deberá agregar procesos lógicos o verificaciones visuales para los pasos que lo requieran. Estos podrán hacer las pruebas distintas del proyecto, llegando a examinar cada uno de los elementos y fases del diseño. Como mínimo, el usuario debe llegar a conocer cual es el error o los errores como resultados. Esto permitirá corregir cualquier elemento anterior.

La complicación principal que debe considerarse es si resulta un error en una etapa avanzada. Por ejemplo, sea DRC, LVS, u otra prueba avanzada en el flujo. Es probable que un elemento de este layout deba ser corregido. Este puede ser un aspecto que no sea modificable desde el diseño original. La solución propuesta es simple, guiar al usuario a abrir la herramienta y corregir el error de manera manual si es que no se puede desarrollar una solución de manera automática. Esto indica la necesidad de poder continuar el sistema de automatización desde un punto medio del flujo de diseño. Si no fuera así, el mismo diseño lógico siempre terminará en el mismo error. Se tendría que iniciar desde el inicio, o continuar el proceso de manera manual desde ese punto.

Un aspecto importante a considerar es que una automatización de este diseño sería altamente dependiente de la complejidad que se le demanda. Con esto se refiere a la posibilidad de un circuito con una gran cantidad de gates, nodos, entre otros. Un programa teórico que realice todas las secciones del flujo de diseño tendría que tener elementos muy específicos a correr. Sería difícil generalizar casos complejos. Sin embargo, se pueden generalizar casos más simples, también con el propósito de poder educar sobre el flujo de diseño.

## CAPÍTULO 8

### Requerimientos y uso de automatización

La mayoría de los procesos individuales de este flujo de diseño fueron explorados y optimizados por los compañeros de trabajo de este último año. Este equipo entregó sus reportes específicos en enero 2022. Existe una gran ventaja en la construcción de este reporte durante la primera mitad del año 2022. Esta es que se podía utilizar estos reportes y trabajos de graduación como referencias para filtrar errores. Por medio de este proceso, se decidió replicar el proceso de cada uno de estas secciones, esta vez desde una sola computadora con un solo usuario.

Por supuesto, se desea simplificar lo más posible este proceso para un usuario final. El sistema implementado en su final requiere solamente los conocimientos mínimos de *Linux*, solamente el conocimiento de como abrir una terminal y ejecutar un *script* con *sh* o preferiblemente *bash*. Para referencias de personas que no conocen esto, esta se detalla a continuación. Desde *linux* se puede abrir el archivo que contiene estos scripts. Con un clic derecho, se puede elegir la opción de "*Open In Terminal*". Esto abre un cuadro adicional que se prepara para recibir comandos. Se puede utilizar las siguientes líneas para ejecutar uno de estos scripts:

Listing 8.1: Ejecución de scripts .sh desde el fólder que los contiene

```

bash auto_logicsyn.sh #Sintesis Logica

bash auto_physicsyn.sh #Sintesis Fisica

bash auto_antenna.sh #Verificacion de antena

bash auto_LVS.sh #Verificacion Layout versus Schematic

bash auto LPE.sh #Extraccion de componentes parasitos

```

Si estas se ubican en distintas ubicaciones al archivo donde se abrió la terminal, es probable que se requieran utilizar direcciones relativas. Con esto se refiere a añadirles símbolos para hacer referencia al lugar de los archivos respectivos. Una terminal no puede encontrar un archivo si no se le dice donde está. Entonces, para futura referencia, se deja un ejemplo de como se modifican estos comandos para ejecutar estos sistemas si se abre la terminal desde el archivo principal del chip que se desea diseñar.

Listing 8.2: Ejecución de scripts .sh desde un fólder superior

bash ./Lvs/auto\_Lvs.sh #Sintesis Logica

bash ./ANTENNA/auto\_antenna.sh #Verificacion de antena

bash ./Lvs/auto\_Lvs.sh #Verificacion Layout versus Schematic

bash ./Lpe/auto Lpe.sh #Extraccion de componentes parasitos

Un problema común que se ha dado en estos trabajos, o más bien una recomendación que los autores han dejado es "ser ordenado". Esto se debe al hecho que la gran mayoría de los programas utilizados en la metodología generan una gran cantidad de archivos. Por ejemplo, StarRC genera documentos de registros solamente con intentar abrirlo. El programa ni siquiera necesita tener éxito en abrirse para generar archivos. Por lo tanto, se necesita tener un buen sistema de organización.

Para esto, se presenta la necesidad de dividir los archivos en tres categorías:

Cuadro 5: Organización de archivos para automatización

| Folder        | Uso                        | Descripción                                                                                             |

|---------------|----------------------------|---------------------------------------------------------------------------------------------------------|

| PROCESO       | Generales y salidas        | Archivos incluyendo script .sh principal, y salidas a próximo proceso.                                  |

| PROCESO/files | Configuración y temporales | Configuración de procesos<br>y archivos temporales                                                      |

| PROCESO/logs  | Registros y resultados     | Archivos secundarios de proceso para debugging y verificar proceso. Este puede estar vacío para correr. |

Esta clasificación de archivos ha sido de gran utilidad. Se optimizaron estos mismos archivos scripts y los archivos de configuración para utilizar rutas relativas, es decir, utilizando un símbolo "."para representar la ubicación actual, y ".."para referirse a la ubicación superior.

Para actualizar el sistema para un nuevo chip, es recomendado copiar uno de los últimos

directorios de chip diseñado, y modificar los runsets ubicados en cada proceso bajo las carpetas llamada files para tener los nuevos nombres. Se recomienda el uso del siguiente comando:

Listing 8.3: Reemplazo de nombres para archivos en mismo fólder sed  $-\mathrm{i}$  's /NOMBRE ANTERIOR/NOMBRE NUEVO/g ' \*

En teoría, sería posible crear un script que hace esto automáticamente. No es posible garantizar su éxito debido a nombres cortos como  $RAM,\ ALU$  o NOT que reemplazan secciones de comandos importantes.

Una vez hecho eso y después de agregar al runset de LVS las instancias de blackboxes de los módulos según detallado por Jose Ruiz [14], será importante correr el sistema, ingresándole un nuevo archivo de verilog para ver los errores. Sería ineficiente asumir que el circuito complete todas las pruebas desde la primera vez. Es mucho más probable que se requiera modificaciones en configuraciones o de diseño.

# capítulo 9

## Desarrollo de automatización

En este capítulo, se pretende demostrar el método general desarrollado para automatizar cada uno de los procesos involucrados en cada sección del flujo del diseño. Al inicio de cada sección, se mostrará la forma del comando que llama a la herramienta apropiada para ejecutar un archivo script. Este archivo script es distinto para cada proceso, donde se encuentra la información detallada de cada corrida. Cualquier cambio al proceso o a los comandos que deben ser corridos en cada proceso deberán ser modificados dentro del mismo script. Esta automatización hace por suposición que ya se tiene un archivo Verilog que se quiere convertir en un layout apropiado.

Esta sección del reporte deberá ser particularmente útil para debugging o filtrar errores de corrida, al igual que para hacer correcciones en el proceso mientras se aprenda más del flujo desarrollado.

Es importante notar que para facilidad de lectura, se asume que dentro de los símbolos <> se reemplaza por el directorio apuntando al archivo, seguido por una barra diagonal (/), y finalizando con el nombre respectivo de los archivos solicitados. Algunos comandos piden más información que solamente la ubicación y nombre del archivo solicitado.

# 9.1. Síntesis lógica

La herramienta para el uso de la síntesis lógica es *Design Compiler*. A este se le llama y se le dice que ejecute un script con el comando:

```

{\it Listing~9.1:~Automatizaci\'on~Design~Compiler} dc_shell _-f <comandos_sintesis_logica.script>

```

El uso es relativamente sencillo, asumiendo que los comandos tienen toda la información necesaria para realizar la síntesis lógica. Detalles de lo que contienen estos scripts se encuentran en el trabajo correspondiente por Elmer Torres.

Sin embargo, es importante notar la importancia de la creación de un archivo .script para esta sección. Esta contiene todos los comandos necesarios para la síntesis que ordinariamente se ingresarían de manera manual a la consola. Se recomienda utilizar el comando # < Comentariodeinstrucciones > para diferenciar cada una de las secciones mientras se está corriendo, verificar visualmente el estado actual del proceso, y de esa manera facilitar el análisis de errores. Este genera partes redundantes de títulos que no sirven más función que facilitar la lectura. A continuación, se describe el proceso general que debe pasar cada script para realizar la síntesis lógica:

Listing 9.2: Síntesis lógica: Script de automatización (.script)

```

--IMPORTANDO-LIBRERIAS--RELEVANTES:

lappend search path < libs path >

set link library <files.db>

set target library <file.db>

---IMPORTANDO-ARCHIVO-VERILOG:

read file -format verilog {< file.v>}

----REVISION--DE--DISENIO y COMPILAR:--

check design

reset design

set max area 0

compile -map effort high -area effort high

--REPORTES:-

report area

report design

report_power

-OUTPUT:-

write -format ddc -h -o <out.ddc>

write -hierarchy -format verilog -output <out.v>

write sdc <out.sdc>

exit

```

Como se podría observar al correr, los títulos comentados también van a aparecer en la terminal. El propósito de estos es legibilidad, sin causar mayor pérdida de procesamiento. Estos comandos se deben colocar en un archivo .script y luego guardar en una carpeta en donde pueda acceder la información que quiere importar cuando sea corrido desde una terminal. La salida de este proceso son los archivos .ddc, .v, y .sdc que fueron especificados en el último capítulo, tanto para el módulo principal como para los IO. Estos sirven como entradas en la síntesis física. Estos pueden ser verificados por medio de Verdi, sin embargo, esto está afuera del alcance de este trabajo. Esto se puede encontrar en el trabajo siendo realizado por Gerardo Cardoza.

#### 9.2. Síntesis física

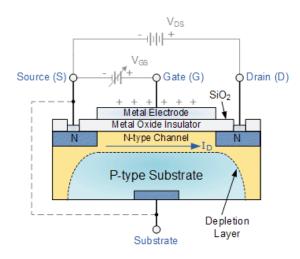

Esta sección viene justamente después de la síntesis lógica, con el siguiente diagrama mostrando los roles que tiene cada programa en el flujo. El rol tomado por Design Compiler es transferir un archivo de HDL (como verilog en este caso) a un diseño descrito por la librería de elección. Este proceso hace lo posible para optimizar tiempos, largos, área, potencia, entre otros. Un análisis puede ser necesario para validar estas propuestas ya que fueron hechas por programa. A continuación, se agrega dicho diagrama para describir la relación entre estos:

Figura 3: DC and ICC Flow [22]

Durante el periodo del proyecto, se realizó una transición importante en las herramientas que estaban siendo utilizadas. Esta transición fue hecha para utilizar *IC Compiler 2* en lugar original de *IC Compiler*. Esto fue hecho debido a las recomendaciones hechas durante el año pasado, donde la versión anterior provocó varias complicaciones en el diseño. [7] A medida que se avanzó en el proyecto, esto demostró ser una sabia decisión.

El comando utilizado en la terminal para ejecutar un script de diseño.

$${\bf Listing~9.3:~Automatizaci\'on~IC~Compiler~II}\\ icc2\_shell~-file~$$

Dentro de IC Compiler 2 es que se hace la conversión del archivo de tipo verilog creado por Design Compiler para preparar archivos de chip que puede ser fabricado. Es importante notar que varios parámetros están fijos en este ejemplo, es probable que sea necesario modificar widths, pitch, o tamaños respectivos dependiendo de la aplicación:

```

Listing 9.4: Síntesis física: Primera parte de command file (.tcl)

<CREACION-LIBRERIA>

1 #--

2 create lib <CIRCUITO SYN.ndm> -technology /usr/synopsys/TSMC/180

Complete/TSMC/180/CMOS/G/stclib/7-track/tcb018gbwp7t 290a FE/

TSMCHOME/digital/Back End/milkyway/tcb018gbwp7t 270a/techfiles/

tsmc018 6lm. tf \

3

-ref libs <TSMCWorkspace.ndm>

4

5

----<IMPORTACION-VERILOG-SINTETIZADO>--

6

read verilog <CIRCUITOio.v>

7

8

read sdc -echo < Logical Synthesis / CIRCUITOio.sdc >

9

10 #--

{\tt read\_parasitic\_tech-tlup\ /usr/synopsys/TSMC/180Complete/TSMC/180/nusperson}

CMOS/G/stclib/7-track/tcb018gbwp7t 290a FE/TSMCHOME/digital/

Back End/milkyway/tcb018gbwp7t 270a/techfiles/tluplus/

t018lo 1p6m typical.tluplus —layermap /usr/synopsys/TSMC/180

Complete/TSMC/180/CMOS/G/stclib/7-track/tcb018gbwp7t 290a FE/

TSMCHOME/digital/Back End/milkyway/tcb018gbwp7t 270a/techfiles/

tluplus/star.map 6M

12

-----<LIMPIEZA-PG>

13 #--

remove pg strategies -all

14

15

16 #--

CMOS/G/stclib/7-track/tcb018gbwp7t 290a FE/TSMCHOME/digital/

Back End/milkyway/tcb018gbwp7t 270a/clf/

MODIFIED antennaRule 018 6lm.tcl"

18

19

------<CREACION-CORNERS>

20

create cell {CORNER1 CORNER2 CORNER3 CORNER4} PCORNER

21

------<\td>VDD-Y-VSS-PADS>-

create cell {PVDD} PVDD1CDG

create_cell {PVSS} PVSS1CDG

24

25

26 #---

27 resolve pg nets

28 create net -power VDD

29 create net -ground VSS

30 connect pg net -net VDD [get pins -physical context *VDD]

connect pg net -net VSS [get pins -physical context *VSS]

32 connect pg net -automatic

```

report cells -power

33 34

```

-----FLOORPLAN-INICIO>--

36 initialize floorplan -site def unit -use site row -keep all -

side length \{285, 285\} -core offset \{125\}

37

39 create io ring -name anillo IO -corner height 115

40

42 #Coloca los pines de entradas y salidas (Pads) en un lugar

arbitrario de no ser especificado en el floorplan

43 add to io guide [get io guides anillo IO.left] PVDD*

44 add to io guide [get io guides anillo IO.right] PVSS*

45 place io

46

47 #----CREACION-ANILLO-PG>---

48 create pg ring pattern ring pattern -horizontal layer METAL2

horizontal width {2} -horizontal spacing {2} -vertical layer

METAL3 -vertical width {2} -vertical spacing {2}

set pg strategy core ring —pattern {{name: ring pattern}}

{

nets: \{VDD\ VSS\}\}\ \{offset: \{1\ 1\}\}\}\ -core

compile pg -strategies core ring

51

53 create pg macro conn pattern hm pattern -pin conn type

scattered pin -layers {METAL2 METAL3} -nets {VDD VSS} -

pin layers {METAL2}

54 set app options —name plan.pgroute.treat pad as macro —value true

set pg strategy macro conn -macros [get cells {PVDD* PVSS*}] -

pattern {{name: hm_pattern} {nets: {VDD VSS}}}}

56 set pg strategy via rule macro conn via rule -via rule {{{{

strategies: macro conn}}{{existing: all} {layers: METAL3}} {

via master: default}} {{intersection: undefined}{via master:

NIL\}\}

57 compile pg -strategies macro conn -via rule macro conn via rule -

tag test

58

60 connect_pg_net -automatic

61 create_pg_mesh_pattern mesh_pattern -layers { {{vertical layer:

METAL3 {width: 4.2} {pitch: 42} {spacing: interleaving}} }

62 set_pg_strategy mesh_strategy -polygon {{125.000 118.000}} {409.480}

414.240}} -pattern {{pattern: mesh pattern}{nets: {VDD VSS}}}

-blockage {macros: all}

63 create pg std cell conn pattern std cell pattern

64 set_pg_strategy std_cell_strategy -core -pattern {{ pattern:

65 compile pg

```

Los comentarios agregados, demostrados por símbolos de numeral (#), ayudan a titular o describir el propósito de cada sección de los comandos. Esta es una costumbre importante ya que por medio de estas definiciones se puede dar una idea de lo que ejecuta cada bloque. En este punto, ya se tiene cargado la gran mayoría de los archivos, permitiendo realizar un análisis, agregando las conexiones restantes hacia afuera del chip, y finalizar las rutas.

Listing 9.5: Síntesis física: Segunda parte de command file (.tcl) -<MERGE-DE-MESH-Y-ANILLO-PG>-1  $2 \text{ merge\_pg\_mesh-nets} \{VDD \text{ VSS}\} - \text{types} \{\text{ring stripe}\} - \text{layers} \{\text{METAL2}\}$ METAL3} 3 ------PLACEMENT-CREACION>--4 5 set app options — name place.coarse.fix hard macros — value false 6 set\_app\_options -name plan.place.auto create blockages -value auto create placement -floorplan -timing driven -congestion -effort high -congestion effort high legalize\_placement 8 9 10 #-----SINTETIZAR-RELOJES>-(Solo chips secuenciales)----11 check clock trees -clocks clk 12 check design -checks pre clock tree stage 13 synthesize\_clock\_trees -clocks clk -postroute -routed clock stage detail with\_signal\_routes 14 clock\_opt -list\_only 15 check design -checks cts qor 16 18 check routability -check pg blocked ports true 19 check design -checks pre route stage 20 route auto 21 ------CORE-FILLER-Y-ANILLO-IO>---create\_io\_filler\_cells -io\_guides [get\_io\_guides {anillo IO.top anillo IO.right anillo IO.left anillo IO.bottom} -reference cells {PFILLER1 PFILLER5 PFILLER05 PFILLER0005 PFILLER10 PFILLER20} create stdcell fillers -lib cells [get lib cells {TSMCWorkspace}] FillersWorkspace/FILL64BWP7T TSMCWorkspace/FillersWorkspace/ FILL32BWP7T TSMCWorkspace | Fillers Workspace / FILL16BWP7T TSMCWorkspace | Fillers Workspace | FILL8BWP7T TSMCWorkspace | FillersWorkspace/FILL4BWP7T TSMCWorkspace/FillersWorkspace/ FILL2BWP7T TSMCWorkspace | Fillers Workspace / FILL1BWP7T } ] 26 connect pg net -automatic 27 remove stdcell fillers with violation 28 check legality

Después de correr la parte anterior, se pueden realizar las pruebas debidas. Sin embargo,

es importante notar que después de estas pruebas, es necesario generar un archivo .gds para las pruebas después. El siguiente comando es capaz de realizar este objetivo:

```

Listing 9.6: Síntesis física: Creación de .gds

write_gds -library <libreria.ndm> -design <TOP_CELL> -view design

-hierarchy all -lib_cell_view frame <CIRCUITO.gds>

```

Sin embargo, antes de generar este gds, es preferible correrlo después de la prueba de DRC. Este se corre en el mismo script .tcl. Se explican como secciones separadas para no sobre complicar la explicación del mismo:

## 9.3. Design Rule Check

Repitiendo la función de este proceso, el propósito de DRC es la verificación de un layout para que este cumpla cada una de las reglas de fabricación, colocando de primera prioridad que el diseño analizado no resulte en problemas inesperados de fabricación o fallas de diseño por error humano. Un ejemplo de las reglas más fundamentales es la separación de nodos con designaciones distintas (es decir, que señales distintas se mantengan separadas), y que esa separación sea lo suficiente para que el efecto que tengan entre sí sea nulo o insignificante.

En este caso, TSMC tiene su reglamento extenso, descrito en detalle y digitalizado en el archivo  $ICVM18\_LM16\_LM152\_6M.215A\_pre041518$  que sirve para informarle al programa de ICV cuales son las reglas utilizadas. Debido al acuerdo de confidencialidad con TSMC, no es apropiado describir cuales son estas en este trabajo. Lo relevante es mencionar que estas son las reglas que fueron utilizadas en este proyecto.

Actualmente, es importante mostrar la forma del comando que *Custom Compiler* utiliza para producir todos los archivos para continuar el proceso. En este ejemplo, se ha generalizado para poder describir lo que se agrega en cada parte del proceso:

```

Listing 9.7: DRC: icv comando para openaccess

```

Como se podría asumir, openaccess se refiere a las librerías preparadas por Synopsys para realizar sus diseños. Estas no son las librerías que fueron utilizadas por este proyecto. El formato anterior simplemente es un guía. Una opción para correr esta prueba es utilizar siguiente comando:

```

\label{eq:condition}  \mbox{Listing 9.8: DRC: icv comando para correr script} \\ \mbox{icv } -\mbox{i } <\!\! \mbox{CIRCUITO\_IO.gds} > -\mbox{c } <\!\! \mbox{nombre-de-celda} > \mbox{ICV } \mbox{vue } <\!\! \mbox{DRC\_RUNSET} > -\mbox{CIRCUITO\_IO.gds} > -\mbox{c } <\!\! \mbox{nombre-de-celda} > \mbox{ICV } \mbox{vue } <\!\! \mbox{DRC\_RUNSET} > -\mbox{CIRCUITO\_IO.gds} > -\mbox{c } <\!\! \mbox{nombre-de-celda} > \mbox{ICV } \mbox{vue } <\!\! \mbox{DRC\_RUNSET} > -\mbox{CIRCUITO\_IO.gds} > -\mbox{c } <\!\! \mbox{nombre-de-celda} > \mbox{ICV } \mbox{vue } <\!\! \mbox{DRC\_RUNSET} > -\mbox{CIRCUITO\_IO.gds} >

```

El método de antena utiliza este mismo comando. Sin embargo, para facilitar el uso de síntesis física al igual de realizar las correcciones debidas, se integra su corrida desde que se está creando las rutas.

El método utilizado al final se hace en medio de síntesis física, desde *IC Compiler 2*, justo después de haber completado las rutas. A continuación, se muestra el final del documento .tcl que fue corrido al inicio de la Síntesis física:

Es relevante notar que en el bloque de script para DRC, también se está realizando una prueba de LVS. Esta funciona como una prueba propia dentro de la herramienta de ICC 2. Esta prueba opera con criterios distintos a los necesarios por TSMC. Debido a esto, todavía resulta necesario correr estas pruebas por medio de ICV directamente.

La sección de reglas de antena es similar a esta. Simplemente definiendo un script de configuración del sistema y corriendo el sistema. Este no requiere mayor explicación, simplemente optimizar el archivo de configuración para correr las reglas de antena. Esta se corre con un solo comando de icv similar al encontrado con DRC y se le ingresa los comandos apropiados.

# 9.4. Layout versus Schematic

La validación de *LVS* se refiere a una comparación entre el diseño propuesto de layout contra el esquemático que soluciona el problema que se desea resolver. Es útil mostrar el uso de *Custom Compiler* para correr LVS. Cada opción está asociada a distintas configuraciones dentro de la herramienta, incluyendo la interfaz gráfica, las librerías utilizadas, el archivo

de *mapping*, configuración del *runset*, entre otros. Es importante notar que este no es el utilizado por la automatización desarrollada, simplemente se agrega como referencia:

#### Listing 9.10: LVS: icv comando para openaccess

```

exec-oa22.60.021.icv icv -f openaccess -i <nombre_libreria> -

oa_view <nombre_de_vista> -oa_lib_defs <archivo_libreria.defs>

-oa_layer_map <archivo_mapping.map> -rc <runset_configuracion>

-s <esquematico.sp> -sf SPICE -stc <root_cell> -sf SPICE -

verbose -oa dm6 -vue <runset> <log name.log> 2>&1

```

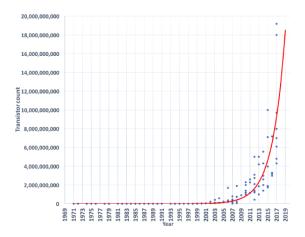

Debido a que en la automatización, no se tienen definidas secciones de librerías o vistas, es necesario encontrar otro método de LVS. La relación entre *IC Validator* y *StarRC* es evidente en la manera que dependen del otro. Esto es porque no es permitido hacer una extracción de parásitos sin antes haber aprobado un LVS. A continuación, se muestra un diagrama describiendo el proceso de ICV para realizar LVS y luego LPE:

Figura 4: ICV and StarRC Flow [18]

Este proceso es descrito con más detalle en el trabajo de José Ruiz. [14]

El primer paso para realizar LVS va a involucrar la traducción de *Netlist*, primero de archivo *Verilog* a *ICV*, y luego de *Verilog* a *SPICE*. Esto se puede realizar con los siguientes dos comandos:

El segundo paso involucra copiar los dichos netlists de StandardCellLibrary y I/OCellLibrary. Estos se definen de la siguiente manera como fue descrito por el trabajo hecho en esta sección:

```

Listing 9.12: LVS segundo paso: Definición de headers Standard Cell Library > CORE. vI/O~Cell~Library~> IO.\,v

```

El tercer paso involucra concatenar estos dos en un archivo *headers.v.* Y esto se puede realizar con el comando *cat*:

```

{\rm Listing~9.13:~LVS~tercer~paso:~Concatenaci\'on~de~headers} cat {\rm CORE.\,v~IO.\,v}~>~h\,eaders\,.\,v

```

El cuarto paso involucra traducir este archivo a CDL o SPICE:

Dicho archivo viene incompleto, y por lo tanto, se le debe agregar las siguientes lineas a su inicio:

```

Listing 9.15: LVS 4.5 Paso: agregado a headers.sp

```

.GLOBAL VDD VSS VDDPST VSSPST

- \*.EQUATION

- \*.SCALE METER

documento.sp>

\*.MEGA

.PARAM

.INCLUDE <source.added>

Cabe mencionar que el archivo de source.added es dado por TSMC, y en general, se puede encontrar en el servidor en la siguiente carpeta

```

/usr/synopsys - old/TSMC/SCRIPTS NUEVOS/20191128 - 124344

```

Pasando al quinto paso, se requiere la creación del archivo .icv, que contiene la netlist de este dispositivo:

```

Listing 9.16: LVS quinto paso: Creación de netlist.icv

```

En este punto existía un sexto paso que involucraba la creación de un archivo .gds para el que era necesario importar la librería de síntesis lógica a CC y exportarlo manualmente. Sin embargo, en el proceso de exploración de las herramientas, se encontró un método para generar el mismo desde la síntesis lógica. Por lo tanto, siempre que este sea completado, se omite el sexto paso de LVS.

Anteriormente, lo que se había hecho es generar este archivo con CC, importando la información debido a  $Custom\ Compiler\ y$  solicitar la generación del archivo desde ahí. Esta solución temporal solucionaba debidamente la generación.

Finalmente, el séptimo paso, luego de realizar una revisión completa del *runset* y de los archivos, es la prueba LVS. Este se puede realizar con un solo comando, utilizando todos los archivos generados durante estos pasos:

```

Listing 9.17: LVS séptimo paso: Prueba de LVS ic v -i <a href="center-color: blue-color: line-color: line-color: blue-color: blue-color

```

Por supuesto, este paso involucra revisar los resultados. Con esta información, y los archivos generados por la herramienta, incluido los reportes involucrados, es posible correr la extracción de parásitos.

# 9.5. Layout Parasitic Extraction

El trabajo hecho originalmente por Charlie Cruz era principalmente de ejecución del método. En esa etapa del proyecto, no fue posible utilizar apropiadamente StarRC, siendo difícil abrir su interfaz gráfica. Por lo tanto, Cruz se dedicó a establecer un método para ejecutar LPE por medio de CC.[5] Por lo tanto, durante este tiempo, se saltó inmediatamente a automatizar este proceso, ya que el programa independiente operaba correctamente. Esto se sabía porque CC hace la llamada a StarRC. Fue originalmente basado en este proceso en el que se ubicó el método de automatización que ya hizo posible durante este periodo independizarse de  $Custom\ Compiler$ .

El comando utilizado para realizar una extracción de parásitos, con toda la información completa es:

```

\label{listing 9.18: Automatizacion StarRC} Let $$\operatorname{StarXtract}$ < \operatorname{comandos\_LPE.cmd} > < \log_n name. \log > 2 > \&1

```

Como fue explicado anteriormente, el proceso LPE es principalmente realizar un análisis de componentes del layout. Este utiliza la información del layout para generar un *netlist*, o más bien un documento descriptivo para usarse en *HSPICE*. Este documento describe a detalle cada una de las capacitancias y resistencias parásitas. Estas se refieren a las interacciones accidentales que surgen no por agregar elementos, sino por naturaleza de la física en el diseño del layout.

Información de este proceso se puede encontrar en el trabajo hecho por Charlie A. Cruz [5]. Con eso aclarado, es importante aclarar varios detalles generales. La herramienta de *Synopsys* optimizada para el proceso de *LPE* es *StarRC*. Este tiene como entrada información general del proceso de LVS y el layout, produciendo un documento con la capacidad de describir el comportamiento verdadero de un chip con dicho layout de la manera más exacta posible.

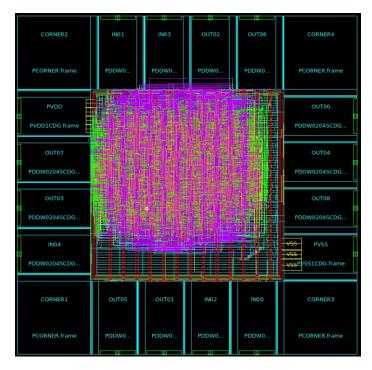

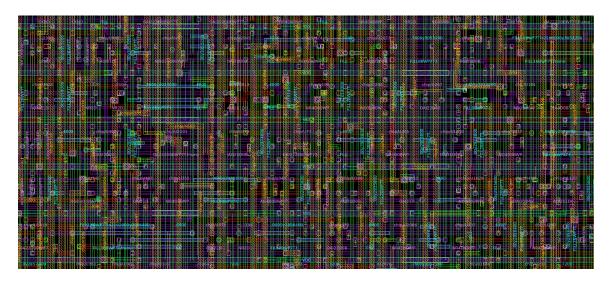

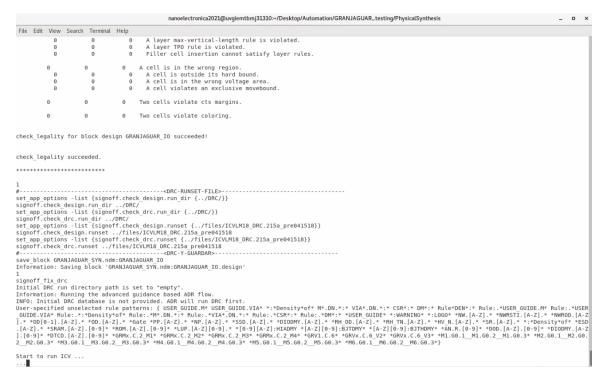

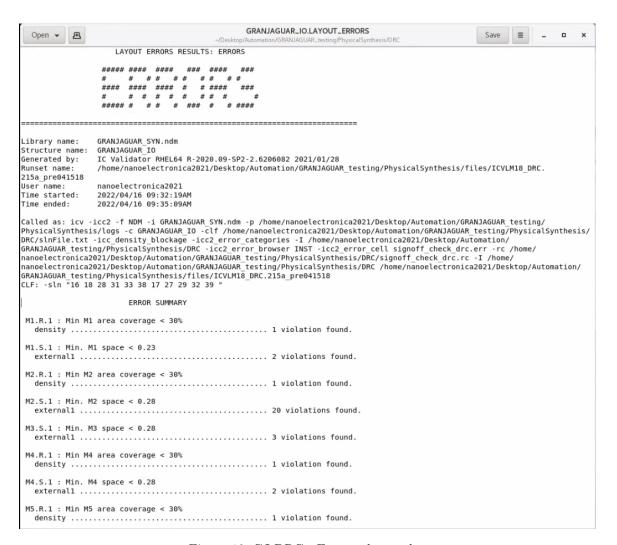

Este es un paso crucial para el diseño de cualquier chip. Un diseño de layout podría pasar correctamente la prueba de DRC y LVS, representando un seguimiento correcto de las reglas de diseño y además una similitud exacta al esquemático diseñado. Sin embargo, el comportamiento del circuito puede ser modificado por las capacitancias y resistencias agregadas por imperfecciones del material o interacciones entre vías y componentes. En el mejor caso, estas podrían simplemente alentar las respuestas del circuito con capacitores que deben ser cargados para cambios de voltaje y resistencias que modificar su información. Este efecto podría ser considerable, incluso requiriendo un nuevo diseño para cumplir las necesidades del diseño. Esto muestra la importancia de esta verificación.