# UNIVERSIDAD DEL VALLE DE GUATEMALA

Facultad de Ingeniería

# Diseño y desarrollo de ADC cíclico con tecnología de 32 nm

Trabajo de Graduación presentado por

**Ennio Antonio Guzmán Colmenares**

para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala

2018

| (f) | ARO                  |  |

|-----|----------------------|--|

|     | (Msc. Carlos Esquit) |  |

Tribunal Examinador:

(f) (Ing. Jonathan de los Santos)

Fecha de aprobación: Guatemala 14 de noviembre de 2018

# Diseño y desarrollo de ADC cíclico con tecnología de 32 nm

# UNIVERSIDAD DEL VALLE DE GUATEMALA

Facultad de Ingeniería

# Diseño y desarrollo de ADC cíclico con tecnología de 32 nm

Trabajo de Graduación presentado por

**Ennio Antonio Guzmán Colmenares**

para optar al grado académico de Licenciado en Ingeniería Electrónica

Guatemala

2018

# ÍNDICE

|                                             | Pagina |

|---------------------------------------------|--------|

| LISTA DE GRÁFICOS                           | viii   |

| LISTA DE TABLAS                             | xi     |

| RESUMEN                                     | iv     |

|                                             |        |

| Conítulos                                   |        |

| Capítulos                                   |        |

| I. Introducción                             | 1      |

| II. Objetivos                               | 4      |

| A. Objetivo general                         | 4      |

| B. Objetivos específicos                    | 4      |

| III. Justificación                          | 5      |

| IV. Marco teórico                           | 6      |

| A. Características de rendimiento de un ADC | 6      |

| 1. Características generales                | 6      |

| 2. Tipos de errores en un ADC               | 10     |

| 3. Parámetros de ruido en ADCs              | 18     |

| 4. Sobre muestreo                           | 21     |

| 5. Tiempos en un ADC                        | 21     |

| B. Otras arquitecturas de ADC               | 22     |

| 1. ADC Flash                                | 22     |

| 2. ADC de aproximaciones sucesivas (SAR)    | 23     |

|      | 3. ADC rampa o integrador                                                   | 24        |

|------|-----------------------------------------------------------------------------|-----------|

|      | 4. ADC tipo Pipeline                                                        | 24        |

| (    | C. ADC cíclico                                                              | 25        |

| V.   | Delimitación y alcances del diseño                                          | 28        |

| VI.  | I. Metodología                                                              | 29        |

| VII. | II. Diseño del sistema                                                      | 32        |

| A    | A. Contador digital                                                         | 32        |

|      | 1. Circuitos que componen este módulo                                       | 32        |

|      | 2. Contador digital de tres bits                                            | 43        |

| E    | B. Comparador digital                                                       | 46        |

| (    | C. Circuito Shift Register y memoria                                        | 49        |

|      | D. Comparador analógico                                                     | 50        |

| E    | E. Circuito sujetador de señales                                            | 54        |

| F    | F. Circuito ajustador de señales                                            | 57        |

| VIII | III. Resultados                                                             | 60        |

| IX.  | . Discusión de resultados                                                   | 68        |

| X.   | Conclusiones                                                                | 74        |

| XI.  | I. Recomendaciones                                                          | 75        |

| XII. | II. Bibliografía                                                            | 76        |

| XIII | III. Apéndice                                                               | 79        |

| Þ    | A. Especificaciones de transistores MOSFET de tecnología de 50 nm utilizado | s en este |

| ķ    | proyecto                                                                    | 79        |

| E    | B. Especificaciones de transistores MOSFET de tecnología de 32 nm utilizado |           |

| r    | provecto                                                                    | 81        |

| C.     | Resultados de corrida de los 256 posibles valores de conversión | .84 |

|--------|-----------------------------------------------------------------|-----|

| D.     | Programa en python para revisión resultados de ADC              | .91 |

| XIV. G | Glosario                                                        | .96 |

# LISTA DE GRÁFICOS

| Dí. | •   |

|-----|-----|

| Pad | ına |

| - 3 | _   |

| Figura No.1.  | Diagrama de bloques del ADC cíclico          | 2  |

|---------------|----------------------------------------------|----|

| Figura No.2.  | Diagrama de bloque de un ADC                 | 6  |

| Figura No.3.  | ADC de entrada única                         | 7  |

| Figura No.4.  | ADC de entrada diferencial                   | 8  |

| Figura No.5.  | Función de transferencia de un ADC ideal     | 9  |

| Figura No.6.  | ADC perfecto de una entrada única            | 10 |

| Figura No.7.  | Error de offset positivo                     | 11 |

| Figura No.8.  | Error de offset negativo                     | 12 |

| Figura No.9.  | Error de ganancia positivo                   | 13 |

| Figura No.10. | Error de ganancia negativo                   | 13 |

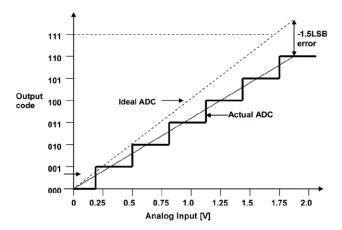

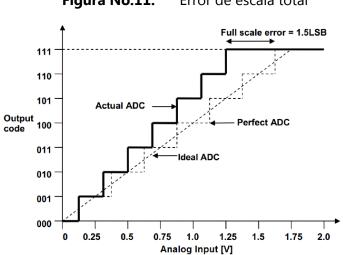

| Figura No.11. | Error de escala total                        | 14 |

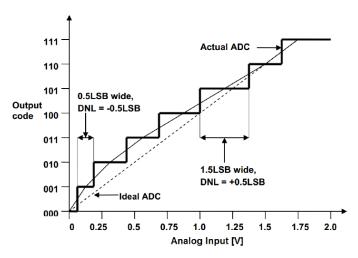

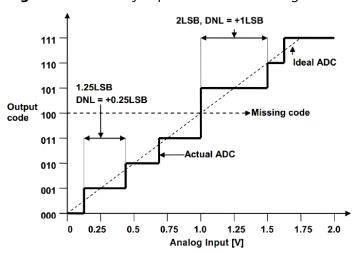

| Figura No.12. | No linealidad diferencial (DNL)              | 15 |

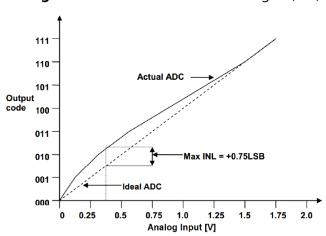

| Figura No.13. | No linealidad integral (INL)                 | 16 |

| Figura No.14. | Ejemplo de ADC con códigos faltantes         | 17 |

| Figura No.15. | Espurios en una señal de entrada a 10 MHz    | 20 |

| Figura No.16. | Diagrama de ADC tipo Flash                   | 23 |

| Figura No.17. | Arquitectura ADC SAR                         | 24 |

| Figura No.18. | Diagrama de flujo de ADC cíclico             | 26 |

| Figura No.19. | Diagrama de bloques ADC cíclico convencional | 27 |

| Figura No.20. | Diagrama de flujo de elaboración de proyecto | 29 |

| Figura No.21. | Esquemática compuerta not                    | 33 |

| Figura No.22.       | Resultados compuerta NOT en LTspice                                     | 34 |

|---------------------|-------------------------------------------------------------------------|----|

| Figura No.23.       | Resultados de compuerta not en Hspice. En negro entra del sistema, e    | en |

| rojo salida del sis | stema                                                                   | 34 |

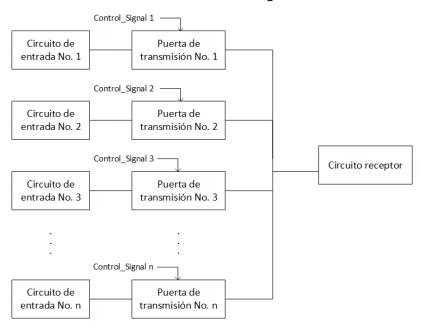

| Figura No.24.       | Conexión de varios circuitos de entrada a través de puertas de          |    |

| transmisión, diag   | ırama                                                                   | 36 |

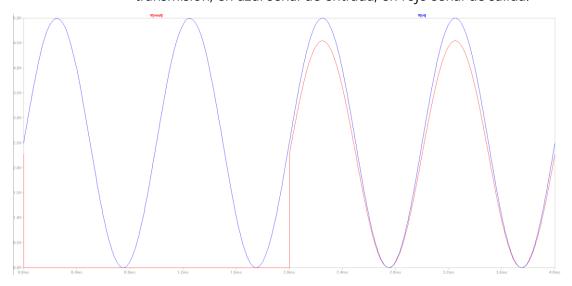

| Figura No.25.       | Gráfica de ejemplo de conexión de varios circuitos de entrada a través  | 5  |

| puertas de transi   | misión                                                                  | 37 |

| Figura No.26.       | Esquemático de circuito puerta de transmisión                           | 37 |

| Figura No.27.       | Resultados, en verde la señal de control, en azul la señal de entrada y | en |

| rojo la señal de s  | alida                                                                   | 38 |

| Figura No.28.       | Error por dimensionamiento de los transistores en puertas de            |    |

| transmisión, en a   | zul señal de entrada, en rojo señal de salida                           | 39 |

| Figura No.29.       | Correcto dimensionamiento de transistores en puertas de transmisión     | ۱. |

| En azul señal de    | entrada, en rojo señal de salida                                        | 39 |

| Figura No.30.       | Esquemático flip-flop tipo D                                            | 40 |

| Figura No.31.       | Esquemático de un flip flop tipo D a partir de latches                  | 41 |

| Figura No.32.       | Gráfica de funcionamiento de un latch                                   | 41 |

| Figura No.33.       | Funcionamiento correcto de flip-flop tipo D. En rojo señal de CLK, en   |    |

| negro señal D y e   | en azul señal Q                                                         | 42 |

| Figura No.34.       | Funcionamiento incorrecto de flip-flop tipo D. En azul señal de CLK, el | n  |

| verde señal D y e   | en rojo señal de Q                                                      | 43 |

| Figura No.35.       | Circuito contador de 3 bits                                             | 44 |

| Figura No.36.       | Resultados circuito contador. En corinto señal clk, en rosado bit 0, en |    |

| azul bit 1 y en ro  | jo bit 2                                                                | 44 |

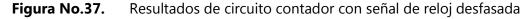

| Figura No.37.       | Resultados de circuito contador con señal de reloi desfasada            | 45 |

| Figura No.38.                  | Concepto comparador implementado                                           | .46            |

|--------------------------------|----------------------------------------------------------------------------|----------------|

| Figura No.39.                  | Esquemático comparador digital                                             | 47             |

| Figura No.40.                  | Esquemático AND de tres entradas                                           | 47             |

| Figura No.41.                  | Esquemático AND de dos entradas                                            | 48             |

| Figura No.42.                  | Esquemático de circuito shift register y memoria                           | 50             |

| Figura No.43.                  | Esquemático de circuito ideal de comparador analógico                      | 51             |

| Figura No.44.                  | Comparador implementando opamp con transistores de 50 nm                   | 52             |

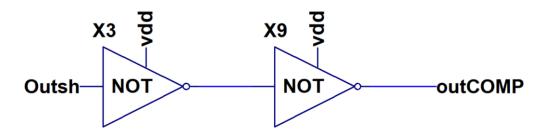

| Figura No.45.                  | Circuito comparador usando doble inversor                                  | 53             |

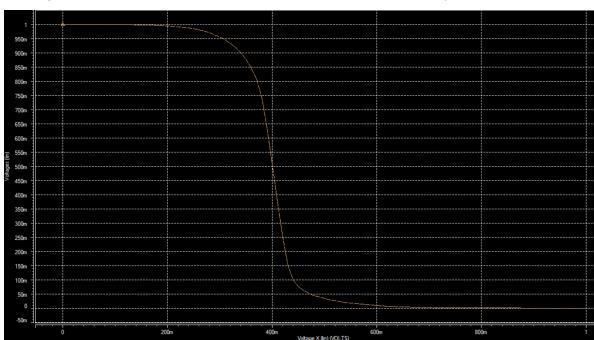

| Figura No.46.                  | Análisis AC inversor con error de corrimiento y pendiente en Hspice        | 54             |

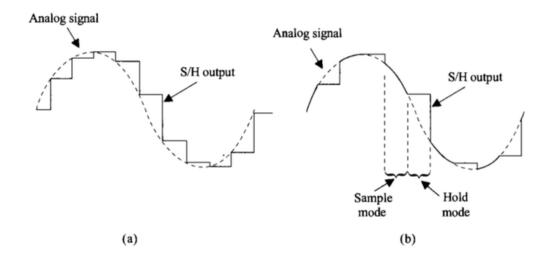

| Figura No.47.                  | Salida de (a) circuito S/H ideal y (b) circuito track and hold (T/H)       | 56             |

| Figura No.48.                  | Esquemático circuito muestreador                                           | 57             |

| Figura No.49.                  | Circuito restador                                                          | 58             |

| Figura No.50.                  | Esquemático de circuito ajustador de señales                               | 59             |

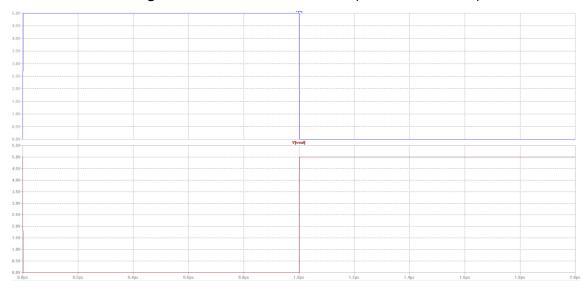

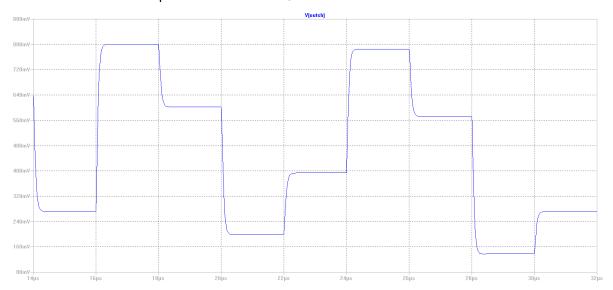

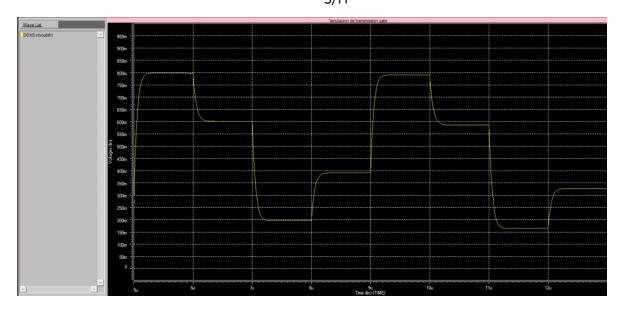

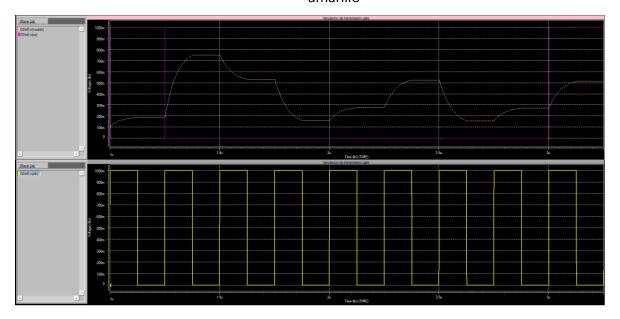

| Figura No.51.                  | Simulación en LTspice de ADC cíclico con circuitos analógicos ideales,     |                |

| conversión de 80               | 0 mV @ 125 kHz                                                             | 60             |

| Figura No.52.                  | Simulación en LTspice de ADC cíclico con amplificadores operacionale       | <del>!</del> S |

| ideales, conversió             | on de 800 mV @ 125 kHz                                                     | 61             |

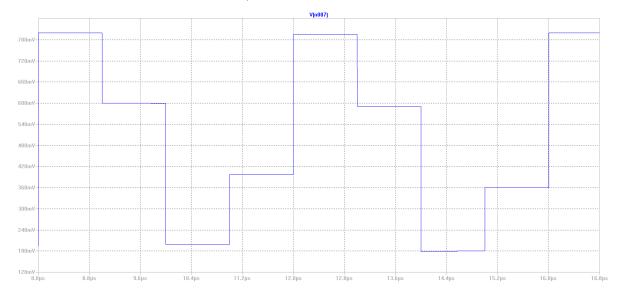

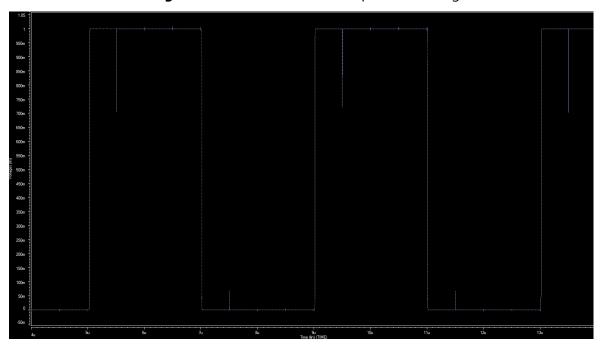

| <b>Figura No.53.</b><br>S/H 61 | Resultados de máxima tasa de conversión, señal de salida del circuito      |                |

| Figura No.54.                  | Contador digital de tres bits, en rojo señal de reloj, en amarillo señales | S              |

| de bit 0, bit 1 y b            | it 2 del contador                                                          | 62             |

| Figura No.55.                  | Salida de comparador analógico                                             | 62             |

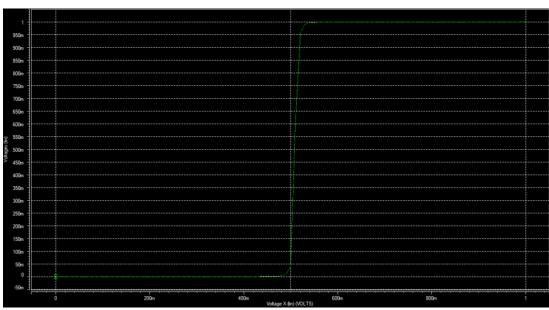

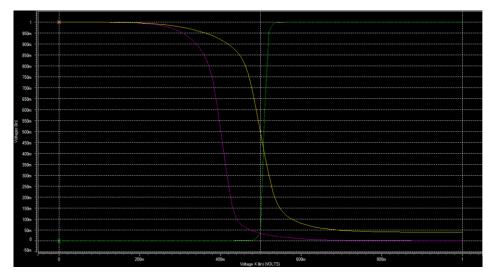

| Figura No.56.                  | Curva DC de inversores utilizados como comparador analógico                | 63             |

| Figura No.57.                  | Salida de comparador digital; en amarillo señales de contador; en azul     | I              |

| señal para indica              | r nuevo muestreo; en rojo señal para copiar del shift register a la memo   | oria           |

|                    |                                                                      | 63   |

|--------------------|----------------------------------------------------------------------|------|

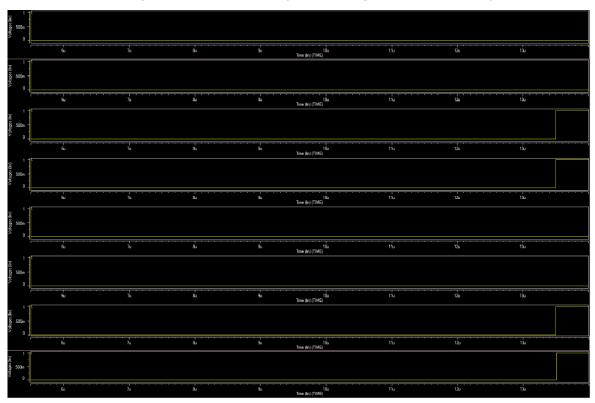

| Figura No.58.      | Resultados de conversión en subcircuito memoria, siendo el LSB la    |      |

| gráfica de hasta a | arriba y el MSB la gráfica de hasta abajo                            | 64   |

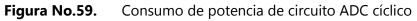

| Figura No.59.      | Consumo de potencia de circuito ADC cíclico                          | 65   |

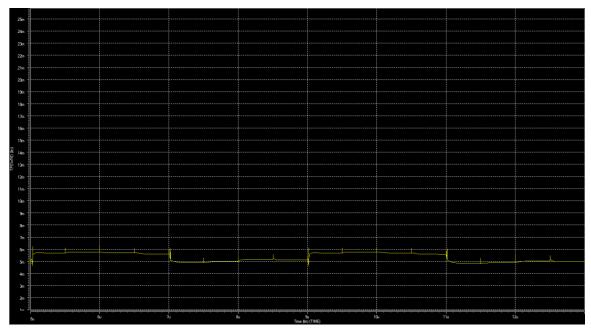

| Figura No.60.      | Simulación de ADC cíclico implementando tecnología de 32 nm al       |      |

| diseño actual, sei | ñal de salida de circuito S/H                                        | 65   |

| Figura No.61.      | Gráfica conversión de función aleatoria, resultados obtenidos vs     |      |

| resultados espera  | ados                                                                 | 67   |

| Figura No.62.      | Etapas de conversión en salida del S/H (café) con error por tasa de  |      |

| conversión inade   | cuada, señal de nueva conversión en morado y señal de reloj en amari | illo |

|                    |                                                                      | 68   |

| Figura No.63.      | Análisis DC de comparador e inversores que lo componen, en amarill   | 0    |

| análisis DC de pr  | imer inversor; en morado análisis DC de segundo inversor; en verde   |      |

| análisis DC de los | s dos inversores en serie                                            | 70   |

# LISTA DE TABLAS

|             | F                                                                  | Página |

|-------------|--------------------------------------------------------------------|--------|

| Tabla No.1. | Tabla de verdad de compuerta NOT                                   | 33     |

| Tabla No.2. | Tabla de verdad circuito de puerta de transmisión                  | 35     |

| Tabla No.3. | Resultados de simulación de ADC cíclico con una entrada de 800mV ( | @ 125  |

| Ksps        |                                                                    | 66     |

| Tabla No.4. | Resultados de corrida de los 256 valores posibles de conversión    | 84     |

# Listado de abreviaciones

**ADC** Convertidor analógico a Digital (Analog to digital converter)

**DAC** Convertidor digital a analógico (Digital to analog converter)

**CMOS** Complementary Metal oxide Semiconductor

**DNL** Diferencial no lineal

**ENOB** Número efectivo de bits

**INL** No linealidad integral

**LSB** Bit menos significativo

**MOSFET** Metal Oxide Semiconductor Field-Effective Transistor

MSB Bit más significativo

**NMOS** n-channel MOSFET

**PMOS** p-channel MOSFET

**S/H** Sample and hold (muestrador)

**SAR** Registro sucesivo de aproximaciones

**SINAD** Señal a ruido y distorsión de radio

**SNR** Radio de señal a ruido

**THD** Distorsión total harmónica

**Opamp** Amplificador operacional

**Vin** Voltaje de entrada

**Vout** Voltaje de salida

# **RESUMEN**

Los convertidores de señales de analógicas a digitales (ADC) han sido muy importantes desde el desarrollo de las computadoras, estos son fundamentales en la interconexión de una computadora con el mundo exterior, sin estos una computadora no tendría noción del entorno. Los ADC son desarrollados utilizando otros subcircuitos, como lo son los amplificadores operacionales, comparadores, flip-flops, contadores, etc., fabricados con transistores, capacitores y resistencias.

En este trabajo de graduación se presenta el desarrollo y estudio de un convertidor A/D (analógico a digital) o ADC de tipo cíclico, junto a un diseño en VLSI del ADC. Un aspecto importante de este trabajo consiste en caracterizar el rendimiento de este circuito tomando como medidas de rendimiento más importantes la potencia del circuito, tasa de conversión máxima y precisión.

La idea fundamental de un ADC cíclico consiste en comparar si la señal de entrada es mayor o menor a un valor preestablecido (en este caso 0.5V), el sistema envía un valor de un uno o cero lógico respectivamente a un circuito shift register, luego la señal se reajusta y se retroalimenta (de forma recursiva), el procedimiento es repetido, correspondiendo a un bit menos significativo, hasta alcanzarse la cantidad de veces (n veces) que se hubiese designado previamente. Al final el valor de conversión en binario pasa a una memoria en donde se retiene como salida del ADC durante el tiempo que dure la siguiente conversión.

La finalidad del trabajo consiste en el desarrollo e implementación de una topología de ADC, con una tecnología de 50 nm, que compruebe los alcances de un ADC cíclico y que pueda servir para futuras investigaciones con diferentes tecnologías o con mejoras que hagan la topología más robusta en diferentes aspectos.

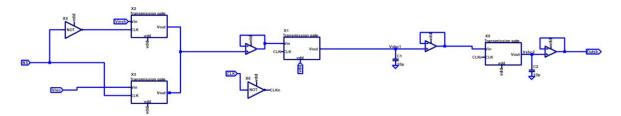

El proyecto se dividió en siete módulos para abstraer y concentrarse mejor en el funcionamiento de cada bloque por individual, estos módulos son los siguientes: Circuito contador, circuito comparador de conteos, circuito sujetador de señales, circuito comparador, circuito shift register, circuito de memoria (banco de memoria) y circuito ajustador de señales.

# I. Introducción

Los convertidores de señales analógicas a señales digitales ADCs actúan como interfaz entre el mundo real "analógico" y el mundo digital. Siempre serán necesarios e irán evolucionando para poder estar adaptados a las tecnologías digitales que a su vez evolucionan rápidamente. Existe una gran diversidad de tipos de ADCs, para determinar cuál implementar se observa los requerimientos de rendimiento de la aplicación, como potencia, tasa de conversión y resolución. El presente trabajo consiste en el diseño y simulación de un ADC tipo cíclico con tecnología de 50 nm, que cuente con una resolución de 8 bits.

El proyecto inició con una etapa de investigación y una serie de etapas de diseño para obtener un diseño que tuviera los requerimientos necesarios.

La primera etapa de diseño fue el desarrollo de un diagrama de bloques en donde se modulariza el proyecto y se indica el funcionamiento general de cada bloque, se expresa su modelo matemático, si lo tuviera, y se determina la interconexión de los diferentes bloques. A continuación se pueden observar los diferentes bloques del presente trabajo de graduación

Figura No.1. Diagrama de bloques del ADC cíclico CLK Circuito Contador Memoria Circuito Circuito Shift Comparador de Register Conteos Data Circuito Input Sujetador de Circuito Comparador Señales Circuito Ajustador de Señales

El sistema posee cuatro entradas, siendo estas VDD, VSS, Data input, CLK y 8 bits de salida, correspondientes al valor convertido y estando estos almacenados en la memoria. Consta de siete bloques, de los cuales se puede diferenciar que 4 son digitales y 3 son analógicos. Los bloques que conforman el ADC cíclico son los siguientes:

- **Circuito contador,** es un circuito digital, recibe la señal de reloj, (llamada CLK), una señal cuadrada que va a una cierta frecuencia que determina la tasa de conversión de cada bit del sistema. Este sistema cuenta cuantos ciclos de la señal de reloj han transcurrido durante cada conversión.

- Circuito comparador de conteos, es un circuito digital, busca levantar una bandera para indicar y ayudar al buen funcionamiento de otros módulos, como es el caso del circuito sujetador de señales que necesita una señal para indicar cuando se inicia la conversión de una nueva señal. Esto a partir de los valores de salida del circuito contador.

- Circuito sujetador de señales, es un circuito analógico, este muestrea y retiene una señal de entrada analógica por cierto tiempo definido, luego de eso vuelve a muestrear una nueva señal.

- Circuito comparador, es un circuito analógico, este circuito compara si la señal es

- mayor o menor que cierto voltaje. Su salida es una señal digital que indica si es mayor o menor respectivamente.

- Circuito Shift Register, es un circuito digital. Este circuito recibe los datos digitales del comparador. Corre un bit con cada señal de reloj, para ir formando la palabra que corresponde al valor digital de la señal inicial a convertir.

- **Memoria**, es un circuito digital. Recibe la palabra del valor de la conversión del circuito shift register. Conecta la salida del ADC con otros circuitos externos.

- Circuito Ajustador de Señales, es un circuito analógico. Opera la señal de entrada según indique el circuito comparador para retroalimentar al circuito ajustador de señales.

# II. Objetivos

# A. Objetivo general

Desarrollar un convertidor analógico a digital tipo cíclico en VLSI utilizando una tecnología de 50 nm

# B. Objetivos específicos

- Caracterizar circuito ADC cíclico para obtención de métricas para tecnología de 50 nm

- Utilizar las herramientas de software de simulación Hspice para el diseño e implementación en VLSI en tecnología de 50 nm.

- Desarrollar un primer circuito VLSI analógico en el departamento de ingeniería electrónica en la universidad del Valle de Guatemala.

- Realizar un ADC cíclico de 8 bits de resolución en tecnología de 50 nm.

# III. Justificación

En la actualidad cualquier sistema que procese información del mundo físico requiere un convertidor analógico a digital. Estos sistemas necesitan diferentes medidas de rendimiento para satisfacer los requisitos mínimos y cumplir con una funcionalidad respectiva. El uso de estos sistemas se ha incrementado con el avance exponencial que presenta la tecnología actualmente. Estos sistemas de procesamiento se ubican en una gran serie de aplicaciones, como lo es la biomédica, aplicaciones del internet de las cosas, instrumentación industrial, robótica, etc. La alta demanda, los avances en dichas áreas y las múltiples aplicaciones en los que se necesitan estos convertidores hace que sea necesario un constante avance tecnológico en este circuito en particular.

El hecho de probar nuevas alternativas de arquitectura da lugar a encontrar particularidades inesperadas, en este proyecto se pretende buscar medidas de rendimiento de dicho circuito y de este modo poder sugerir de forma más sólida en que aplicación se aprovecharía mejor.

En la Universidad del Valle de Guatemala, en el departamento de ingeniería electrónica, se ha estado realizando investigación sobre el VLSI para diferentes tipos de aplicaciones. Sin embargo, en el diseño de circuitos analógicos en VLSI se encuentra muy poco contenido. Por lo que con este trabajo de graduación se busca colocar a Guatemala y a la Universidad del Valle de Guatemala en dicho ámbito de investigación científica.

# IV. Marco teórico

# A. Características de rendimiento de un ADC

# 1. Características generales

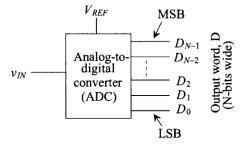

Un ADC es un sistema o módulo que posee una entrada analógica, un voltaje de referencia de entrada (V<sub>REF</sub>) y salidas digitales. Un ADC convierte una señal de entrada analógica en un valor digital, como salida, que representa la magnitud o valor del voltaje de entrada en comparación del voltaje de referencia (V<sub>REF</sub>). Muestrea el voltaje analógico de entrada y produce un código digital como salida para cada muestra realizada.

**Figura No.2.** Diagrama de bloque de un ADC

El <u>voltaje</u> de referencia ( $V_{REF}$ ) es un voltaje que determina el rango de conversión con el cual en voltaje de entrada analógico tiene que ser medido.  $V_{REF}$  puede ser una entrada de voltaje proveniente del exterior. Algunos ADCs son capaces de generar su propio  $V_{REF}$ .

El <u>voltaje analógico de entrada</u> (V<sub>IN</sub>) es el voltaje por medir y convertir a un valor digital. Esta señal siempre debe ser menor o igual a V<sub>REF</sub> para evitar que se sature el ADC. El rango de voltaje es llamado rango de conversión. Dependiendo del número de entradas analógicas se puede clasificar a los ADCs como de entrada única o entrada diferencial.

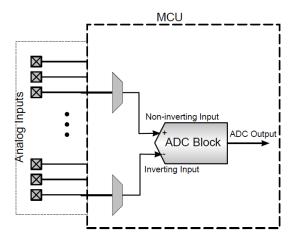

En un ADC de entrada única, el muestreo y la conversión pueden ser realizados únicamente en una señal de analógica a la vez. Se muestra esto en el siguiente diagrama de bloques en la Figura No.3.

Figura No.3. ADC de entrada única

MCU

ADC Block

ADC Output

En el de entrada diferencial, la diferencia en voltaje de las dos (o más) entradas analógicas es procesado en el módulo del ADC. Esto puede ser realizado directamente o después de una etapa de amplificación. Por ejemplo, en el caso dos entradas analógicas,  $A_{in1} = 1.5 \text{ V y } A_{in2} = 0.7 \text{ V}$ , el valor diferencial corresponde a  $0.8 \text{ V } (A_{in1} - A_{in2} = 0.8 \text{ V})$ , el cual es posteriormente convertido a un valor digital.

**Figura No.4.** ADC de entrada diferencial

La mayoría de ADCs pueden operar solamente usando voltajes positivos de entrada. Los ADCs que permiten rangos positivos,  $(0 < A_{in} < V_{REF})$  son llamados ADCs unipolares. Los ADCs capaces de aceptar voltajes tanto positivos como negativos son llamados ADCs bipolares. Por ejemplo, en un ADC unipolar, si el  $V_{REF} = 2V$ , entonces  $0 < A_{in} < 2V$ . En este proyecto se desarrolla un ADC unipolar de entrada única.

El rango total de entrada (0V a  $V_{REF}$ ) está dividido en un número de sub-rangos llamados estados o pasos. Un estado es llamado LSB (bit menos significativo, least significant bit), el número de estados es definido por  $2^N$ . Donde N es llamado la resolución del ADC. Para un  $V_{REF}$  específico, el estado es determinado por la resolución ( $\frac{V_{REF}}{2^N}$ ). Por ejemplo, un ADC con resolución de 3 bits y un  $V_{REF}$  = 10 V, tiene un número total de 8 estados y el tamaño de cada estado es de 1.25.

La cuantificación es un proceso donde la señal de entrada analógica muestreada va a ser reemplazada, empleando una aproximación, por un número finito de valores discretos. Se hace un redondeo de la señal. El LSB se determina si la tensión analógica de entrada se encuentra en el escalón más bajo del rango de tensión de entrada.

Por ejemplo, cuando  $V_{REF} = 2V$ , la resolución (N) = 3 bits, el rango total es divido en ocho

pasos. La entrada analógica de 0V a 250 mV es asignada a la misma salida digital con el código 000 y el voltaje de 251 mV es asignado a 001 y así sucesivamente con los otros valores digitales. Este proceso se llama cuantificación.

El paso de cuantificación (q) está dado de la siguiente forma:

$$q = \frac{V_{REF}}{2^N} = LSB$$

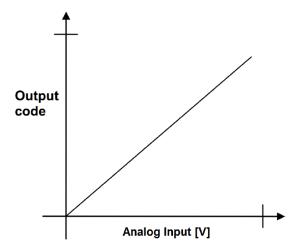

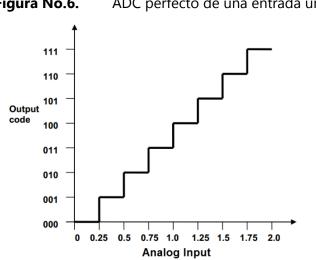

Cuando la resolución de un ADC específico es infinita, se le dice que es un ADC ideal. En otras palabras, la resolución de un ADC ideal es igual al número efectivo de bits (ENOB). En un ADC ideal, todos los posibles valores de entrada proveen una única salida digital del ADC con un rango específico de conversión. Esto es considerado un concepto teórico que no puede ser realizado. Un ADC ideal puede ser descrito matemáticamente usando una función de transferencia lineal, como se muestra en la Figura No.6.

Figura No.5. Función de transferencia de un ADC ideal

Un ADC genera una salida digital, diciendo eso, se puede decir que no le es posible generar una salida continua de valores, como en el caso del ADC ideal.

El ADC perfecto (por definición) realiza el proceso de cuantificación de forma exacta (perfecta). Esto se refiere a una función tipo escalera como función de transferencia, donde cada etapa es un LSB sin ningún tipo de error.

Figura No.6. ADC perfecto de una entrada única

#### 2. Tipos de errores en un ADC

Para poder entender de mejor forma el rendimiento de un ADC, es necesario comprender como este es afectado por varios tipos de errores en su salida. A continuación, se explicarán varios de estos.

#### Error de offset (compensación) a.

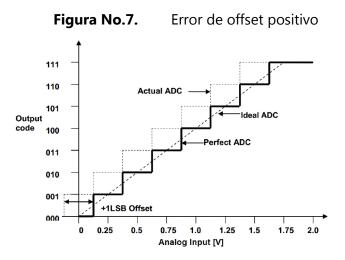

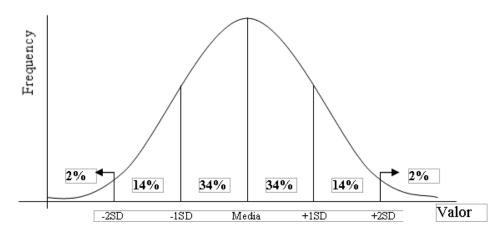

El error por compensación u offset es definido como la variación que existen entre la función de transferencia del actual ADC y el ADC perfecto en el punto cero, medido en el bit LSB. Este puede ser medido en LSB o en voltios. Cuando la transición del valor de salida de 0 a 1 no ocurren en un valor de entrada de 0.5 LSB, entonces se dice que existe un error de compensación (u offset).

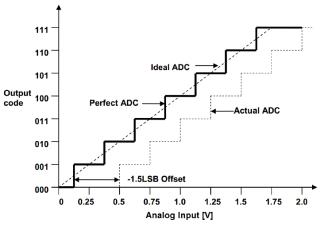

Con un error por compensación positivo, el valor de salida es mayor que 0 cuando la entrada es menor que 0.5 LSB. Con un error por compensación negativo, la entrada es mayor que 0.5 LSB cuando el primer valor de salida ocurre. Se puede explicar de forma más sencilla diciendo que si la función de transferencia actual está por debajo de la del ADC ideal, es un error por compensación negativo, y vise versa. Esto se puede observar mejor en las siguientes gráficas.

En la Figura No.7 se puede observar como la primera transición ocurre en 0.5 LSB y la transición es del valor 001 al valor 010 (de 1 a 2). Esta transición debería de ocurrir en 1.5 LSB para el caso del ADC perfecto. La diferencia (Perfecto – Actual = 1.5LSB – 0.5LSB = +1LSB) es el error por compensación.

**Figura No.8.** Error de offset negativo

En la Figura No.8 se puede observar que la primera transición ocurre en 2 LSB y esta es del valor 000 al valor 001 (de 0 a 1). Esta transición debería de ocurrir en 0.5 LSB para el caso perfecto. Entonces la diferencia (Perfecto – Actual = 0.5 LSB – 2 LSB = -1.5 LSB) es el error por compensación.

# b. Error de ganancia

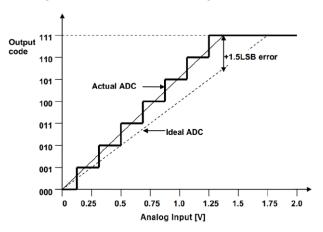

El error de ganancia es definido por la desviación del punto medio del último paso, del actual ADC, con respecto al punto medio del último paso del ADC ideal, después de haber hecho una compensación por el error de offset. Luego de haber descartado el error por offset, introduciendo un voltaje de 0V siempre va a devolver una salida de 000. El error de ganancia causa que la pendiente de la actual función de transferencia se desvíe de la pendiente del ADC ideal. Este error puede ser medido y compensado usando varios valores de salida.

**Figura No.9.** Error de ganancia positivo

**Figura No.10.** Error de ganancia negativo

Si la función de transferencia del ADC actual ocurre debajo de la ideal, entonces se produce un error de ganancia positivo y vise versa. El error de ganancia es calculado en términos de LSB de la línea vertical que se produce entre la pendiente ideal y la actual en el último paso de ambas, como se puede observar en la Figura No.9 y Figura No.10.

En la Figura No.9 se puede observar como el valor de salida se satura antes de que la entrada encuentre su valor máximo.

# c. Error de escala total

Este error es una desviación de la última transición del actual ADC con respecto a la transición del ADC perfecto. Con transición se refiere al tamaño del paso, del cual varia de LSB. Esta medido en términos de LSB o voltios. El error de escala total se debe al error de offset y al de ganancia.

**Figura No.11.** Error de escala total

#### d. No linealidad

Cuando los errores de offset y ganancia son compensados por completo, la actual función de transferencia debería ser igual a la función de transferencia de un ADC perfecto. Sin embargo, la no linealidad de un ADC podría causar que la actual curva se desviara de la curva perfecta, aun si las dos curvas son iguales en cierto punto donde el error de ganancia es medido.

En general existen dos tipos de no linealidades que degradan el rendimiento de un ADC. Estos son la no linealidad diferencial (DNL, differential non-linearity) y la no linealidad integral (INL, integral non-linearity).

# No linealidad diferencial (DNL)

La no linealidad diferencial es definida como la máxima y la mínima diferencia de anchura de un paso entre la actual función de transferencia y la función de transferencia del ADC perfecto. Las no linealidades producen que en la cuantificación de los pasos varié el ancho de estos.

**Figura No.12.** No linealidad diferencial (DNL)

Para el caso del ADC perfecto, el ancho del paso es de 1 LSB. Sin embargo, en un ADC con DNL se puede observar como el ancho de los pasos no es exactamente 1 LSB. En la Figura No.12, en el máximo caso el ancho de un paso llega a ser de 1.5 LSB, para el valor de salida de 101, el DNL en este caso sería de 0.5 LSB. En el caso mínimo, opuesto, el ancho del paso es de 0.5 LSB, para el valor de salida de 001, aquí el DNL es de -0.5 LSB. Por lo que se puede decir de la función de transferencia de la Figura No. 12 que su DNL es de ± 0.5 LSB.

Se puede usar la siguiente ecuación para determinar cada DNL

$$DNL = (D_{cx} - 1)LSBs$$

Donde,  $D_{cx}$  es el tamaño actual de cada paso en LSBs.

# No linealidad integral (INL)

La no linealidad integral es definida como la diferencia máxima vertical entre la curva actual y la ideal, lo cual indica que tanto se ha desviado la curva actual de la ideal. El INL puede ser interpretado como la suma de los DNLs. Por ejemplo, en la Figura No.13 se puede observar que existen múltiples DNLs que generan un INL total positivo. Un INL negativo indica a su vez que está por debajo de la curva ideal. Esto significa que la distorsión de los múltiples DNLs determina la linealidad integral del ADC.

**Figura No.13.** No linealidad integral (INL)

El INL puede ser medido conectando los puntos medios de los pasos de salida de la curva actual y encontrando la desviación máxima de la curva ideal en términos de LSBs. En la Figura No.13 se puede observar como el INL es de 0.75 LSB.

# Falta de códigos

Existen casos en los que no le es posible al ADC generar en su salida algunos códigos, que se dice que son códigos faltantes, esto se puede observar en la mejor en la Figura No.14.

**Figura No.14.** Ejemplo de ADC con códigos faltantes

En la Figura No. 14 se puede observar lo siguiente, el primer código (de 000 a 001) ocurre en los valores de entrada de 250 mV, esto es como lo esperado. En la segunda transición, de 001 a 010 existen entradas que cambian 1.25 LSB, esto es 0.25 LSB más de lo esperado (un DNL de 0.25 LSB). En el siguiente cambio de entrada, en la tercera transición, ocurre que el valor digital de salida se mantiene constante cuando el valor de entrada cambia de 1000 mV a 1500 mV y el código 100 nunca aparece en la salida. Se dice que se pierde ese código.

Los ADCs de alta resolución en varias ocasiones pierden códigos. Un ADC con un DNL menor de ±1 LSB garantiza que no se pierdan códigos.

# e. Error total de desajuste (TUE)

El error total de desajuste representa la máxima desviación entre la función de transferencia del ADC actual y la ideal. Es decir, incluye los errores de cuantificación, offset, ganancia y no linealidad. Este es expresado en LSBs.

$$TUE = \sqrt{e_{offset}^2 + e_{ganancia}^2 + e_{DNL}^2 + e_{INL}^2}$$

#### 3. Parámetros de ruido en ADCs

# a. Relación señal a ruido (SNR)

SNR es definido como la relación entre niveles de voltaje, en RMS, de la señal de salida con respecto del ruido que esta posee. Este es medido en dB. La siguiente fórmula describe la ecuación general para obtener el SNR:

$$SNR(dB) = 20 \log \left( \frac{V_{RMS(Signal)}}{V_{RMS(Noise)}} \right)$$

Además, el valor de SNR de un ADC perfecto es calculado usando la siguiente formula:

$$SNR(dB) = 6.02N + 1.76 (dB)$$

Donde N es la resolución del ADC.

Por ejemplo, un ADC perfecto de 10 bits tendría un SNR de 62 dB. En aplicaciones prácticas, en función de obtener un mayor rendimiento, el SNR del ADC debe ser mayor.

#### b. Distorsión armónica total (THD)

Siempre que una señal de entrada con una frecuencia particular pasa por un sistema no lineal contenido adicional es agregado a los armónicos de la frecuencia original. Por ejemplo, si una señal de entrada contuviera una frecuencia f, los armónicos de esa frecuencia serían 2f, 3f, 4f, etc. El sistema no lineal en el convertidor produciría armónicos que no estuvieran presentes en la señal original. Estas frecuencias armónicas usualmente distorsionan la señal de salida por lo cual se degrada el rendimiento del sistema. El termino de distorsión armónica total describe este efecto.

El THD es definido como la relación de la suma de las potencias de las frecuencias armónicas y la potencia de la frecuencia fundamental, como se puede observar a continuación.

$$THD = \frac{\sum Potencia\ de\ los\ harmónicos}{Potencia\ de\ la\ frecuencia\ fundamental} = \frac{P_1 + P_2 + P_3 + \cdots + P_N}{P_0}$$

En términos de voltaje, en RMS, el THD es de la siguiente forma.

$$THD = \frac{\sqrt{V_1^2 + V_2^2 + \dots + V_n^2}}{V_0}$$

El THD incrementa con el incremento en frecuencia, de la señal de entrada. Mientras la amplitud de la señal de entrada incrementa, la distorsión incrementa. Para obtener mejor rendimiento, es necesario que el valor de THD sea menor.

# c. Distorsión señal a ruido (SINAD)

La distorsión señal a ruido (SINAD) es una combinación de SNR y de THD. Este es definido como la relación entre el valor RMS de la amplitud de la señal y el valor RMS de todos los demás componentes espectrales, incluyendo armónicos. Contiene componentes de ruido y distorsión. Se puede determinar de la siguiente forma:

$$SINAD = -10\log\left(10^{-\frac{SNR}{10}} + 10^{-\frac{THD}{10}}\right)$$

Para obtener un mayor rendimiento, el valor de SINAD de un ADC debería ser mayor.

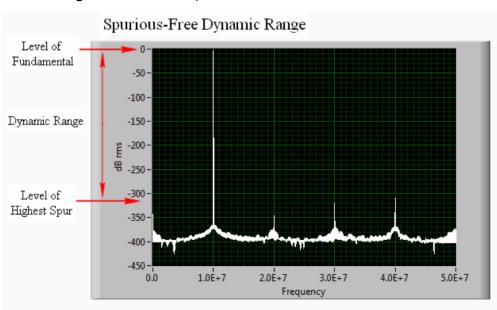

# d. Rango dinámico libre de espurios (SFDR)

Permite caracterizar el desempeño dinámico de una señal. El SFDR describe la relación entre amplitud de la frecuencia dominante y la amplitud de la armónica principal.

Por ejemplo, cómo se puede observar en la Figura No.15, en una señal de entrada con 10 MHz como frecuencia dominante, que hubiera componentes armónicos a 20 MHz, 30 MHz. Estos armónicos se les conoce como espurios.

**Figura No.15.** Espurios en una señal de entrada a 10 MHz

El rango dinámico entre el harmónico dominante y el mayor espurio se le conoce como rango dinámico libre de espurios (SFDR).

El SFDR se puede describir con la siguiente ecuación, en dB

SFDR = Amplitud frecuencia dominante (dB) - Amplitud de espurio más grande (dB)

Del mismo modo se puede describir en términos de voltaje, en RMS.

$$SFDR = 20 \log \left( \frac{Amplitud\ frecuencia\ fundamental\ (RMS)}{Amplitud\ de\ espurio\ más\ grande\ (RMS)} \right)$$

# e. Número efectivo de bits (ENOB)

El número efectivo de bits es el número con el cual el ADC se comporta como un ADC perfecto. Es otra forma de describir el SINAD y se describe con la siguiente ecuación

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

Para tener un mejor rendimiento, el valor de ENOB de un ADC debería ser lo más cercano posible a la resolución del ADC.

#### 4. Sobre muestreo

El sobre muestreo es un proceso que consiste en muestrear a mayor frecuencia que la frecuencia de Nyquist. Entre las diferentes ventajas que conlleva esto se mencionan las siguientes:

- Evita problemas de aliasing

- Provee un modo de incrementar la resolución de un ADC.

- El número de muestreos requiere tener un adicional de n bits es de 2<sup>2n</sup>

- Mejora el SNR de un ADC

Por ejemplo, para implementar un conversor de 14 bits, es suficiente tener un conversor de 14 bits que puede muestrear 256 veces la frecuencia de muestreo con la que contaba previamente el ADC.

# 5. Tiempos en un ADC

En el momento de hacer una conversión, se caracteriza a la conversión con ciertas medidas de tiempo que son importantes, por lo cual serán mencionadas a continuación.

# a. Tiempo de inicio

Contiene el tiempo mínimo que se requiere para hacer la primera conversión desde que el ADC ha sido inicializado.

# b. Tiempo de retención y muestreo

Luego de iniciar la conversión, se requiere que un capacitor mantenga los valores de entrada estables en orden de poder ser convertidos posteriormente. Este es llamado tiempo de muestreo. El número de señales de reloj que requiere para convertir el voltaje muestreado se llama tiempo de retención.

#### c. Tiempo de asentamiento

Es un tiempo observable en el conversor diferencial. Cuando múltiples canales son usados, hay escenarios donde cada canal de ADC tiene diferente ganancia y offset configurados. Cambiar entre estos canales requiere una cierta cantidad de tiempo, antes de empezar la fase de muestreo y retención, en orden de tener resultados acertados puesto si este comenzara antes, se producirían resultados erróneos en la salida del ADC.

#### d. Tiempo de conversión

La suma de los tiempos de muestreo y retención se le conoce como tiempo de conversión. Este es representado en número de tiempos de reloj. Este es el parámetro más importante al decidir la tasa de conversión del ADC.

#### B. Otras arquitecturas de ADC

En esta sección se mencionan varios tipos de arquitecturas de ADC. Se describirán las características principales haciendo un énfasis en las ventajas y desventajas de estos. Se proporcionará una caracterización general de cada tipo de arquitectura.

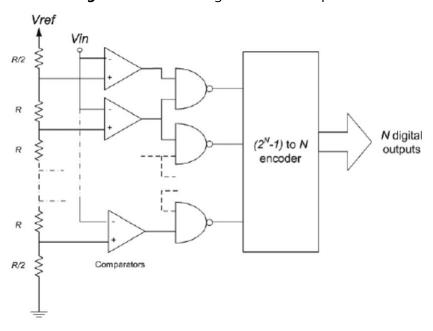

#### 1. ADC Flash

Este ADC es uno de los más comunes. Es la arquitectura de ADC más rápida que existe. Se basa en una serie de comparadores, como se puede apreciar en la Figura No.16, estos comparan todos los niveles de voltaje, estos a su vez pasan a un codificador que proporciona la salida de N bits.

**Figura No.16.** Diagrama de ADC tipo Flash

Entre las características destacadas de esta arquitectura es que solo necesita un tiempo de reloj para hacer la conversión. Por otro lado, necesita  $2^n - 1$  comparadores, lo cual hace que el circuito tenga un área superficial y consumo de potencia muy elevados.

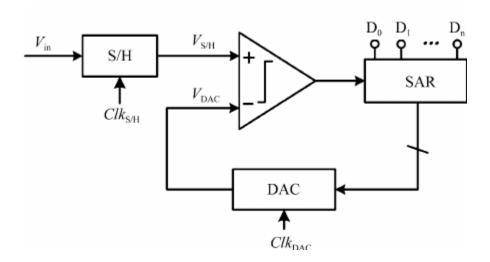

## 2. ADC de aproximaciones sucesivas (SAR)

Esta arquitectura consiste en un ciclo cerrado que empieza con una muestra comparada, siguiendo por un shift register, este está conectado a un DAC y el DAC se compara con la señal comparada originalmente, esto se puede observar en la Figura No.17.

Para esta arquitectura es necesario N ciclos para poder llegar a hacer una conversión. El DAC que contiene incrementa considerablemente la potencia y el área superficial del circuito.

Figura No.17. Arquitectura ADC SAR

### 3. ADC rampa o integrador

Este tipo de arquitectura consiste en generar una señal tipo diente de sierra que tenga una amplitud de todo el rango de conversión. Seguido se compara la señal de entrada con esta señal de diente de sierra. El momento en que las dos señales son iguales, el comparador cambia su señal y se identifica el valor en digital que representa la señal. Por lo general la forma generar la señal de diente de sierra es a partir de un contador seguido de un DAC.

Esta arquitectura posee un tiempo de conversión variable, el cual puede ir de 1 ciclo hasta llegar a  $2^N$  ciclos, donde N es el número de bits del ADC.

### 4. ADC tipo Pipeline

Esta arquitectura consiste dividir la conversión por etapas secuenciales interconectadas. Todas las etapas se realizan en forma paralela, por lo que cada ciclo realiza una conversión.

#### C. ADC cíclico

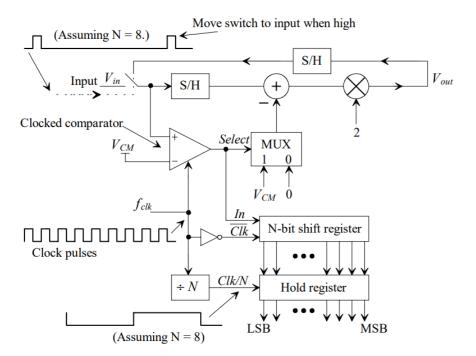

Se puede observar en la Figura No.18 el diagrama de flujo de un ADC cíclico convencional. Este especifica el algoritmo que implementa dicho sistema. Adicionalmente se puede observar en la Figura No.19 el diagrama de bloques del ADC cíclico. En el inicio este sistema muestrea una señal del exterior, llamada V(i) donde i=1 para la primera iteración. Esta señal debe mantener ciertas especificaciones de voltaje y frecuencia para poder realizar la conversión de una forma efectiva. Una conversión tiene N etapas, se utiliza un contador que utiliza una variable, en este caso i, para saber en qué momento termina dicha conversión. Se establece un voltaje llamado V<sub>CM</sub>, el cual se usa como voltaje de comparación en el comparador posteriormente, este debe de ser igual a V<sub>DD</sub>/2. Otro dato importante en este diseño convencional es que la conversión llega a tener un rango de conversión de 0 V a V<sub>REF</sub> V, donde V<sub>REF</sub> = V<sub>DD</sub>.

Luego de tener una señal inicial muestreada prosigue comparar si esta señal es mayor o menor a  $V_{CM}$ , implementando un comparador para esto. Si la señal de entrada del comparador es mayor que  $V_{CM}$ , entonces a la señal de salida del S/H se le resta  $V_{CM}$ . Si la señal de entrada del comparador es menor que  $V_{CM}$ , entonces no se le resta nada a la señal de salida de S/H, esto se puede observar en la Figura No.19, donde un circuito MUX determina como operar la salida del S/H. Posteriormente se multiplica por dos esta señal, para tener una señal  $V(i+1) = 2 \ V(i) - 2 \ V_{CM} \ si fuera el caso que V(i) es mayor que <math>V_{CM} \ y \ V(i+1) = 2 \ V(i) \ si fuera el caso que V(i) fuera menor que <math>V_{CM}$ . Se adiciona un valor al contador de ciclos del sistema (i=i+1). Luego se compara si i<N, si sigue siendo menor a N se prosigue al siguiente ciclo de conversión y se establece que  $V(i) = V \ (i+1)$  antes de empezar este nuevo ciclo.

De forma simultánea en cada ciclo de conversión, la señal de salida del comparador llega a un circuito shift register, donde se va corriendo cada ciclo. En el momento de terminar la totalidad de la conversión una señal le indica a este circuito que pase su

resultado a otro llamado "Hold register" o "Memoria", el cual se comunica con el exterior para dar un resultado de conversión.

Inicio V(1) = Vin, i = 1, Vcm = Vdd/2NO V > Vcm V(i + 1) = 2V(i) - Vcm V(i + 1) = 2V(i)NO V > Vcm V(i + 1) = V(i)

Figura No.18. Diagrama de flujo de ADC cíclico

**Figura No.19.** Diagrama de bloques ADC cíclico convencional

# V. Delimitación y alcances del diseño

En este capítulo se tratará el tema de los alcances que se esperan obtener de este proyecto. Antes del diseño de cualquier sistema es necesario conocer los alcances que se espera conseguir. A continuación, se destacarán una serie de características que se espera que posea el presente proyecto.

Se espera comprobar la efectividad de una metodología de diseño a partir de un prototipado rápido, implementando circuitos ideales analógicos que faciliten la comprobación de la arquitectura. Para luego des abstraer módulos individuales, teniendo un sistema completo funcionando en todo momento. Diseñar en la herramienta Hspice, un ADC cíclico con tecnología de 50 nm. Otro alcance destacado consiste en diseñar un primer prototipo escalable para siguientes versiones con el objetivo de poder llegar a fabricar el circuito ADC en algún momento.

# VI. Metodología

En el presente capítulo se presentará la metodología empleada en los diferentes módulos de diseño del sistema. Para realizar el proyecto fue necesario realizar cuatro prototipos del sistema, los primeros tres prototipos fueron desarrollados en la herramienta LTspice y el cuarto prototipo fue desarrollado en la herramienta Hspice.

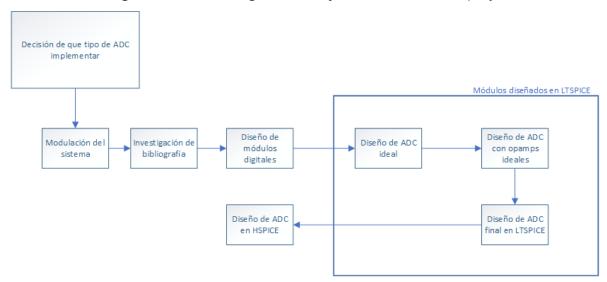

**Figura No.20.** Diagrama de flujo de elaboración de proyecto

Como se muestra en la Figura No.20, la primera etapa, del desarrollo de este proyecto, es la decisión de qué tipo de ADC implementar. La decisión del desarrollo de un ADC cíclico fue lo primero a tomar en cuenta en este proyecto. La elección de esta arquitectura se debe a que ya se contaba con experiencia, en proyectos anteriores, implementándola.

La siguiente etapa del desarrollo es la modulación del sistema. Con esto se refiere a que se divide el sistema submódulos, las cuales se representan en diagramas de bloques, como se puede observar la Figura No.1, está dividido en siete módulos principales, de los cuales cuatro son totalmente digitales y tres son analógicos. Es destacable mencionar que se escogieron estos módulos por su funcionalidad, abstrayendo en sí su respectivo diseño.

La investigación de la bibliografía fue de mucha ayuda para la realización de este proyecto. Con ella se pudo llegar a aclarar la forma en la cual se iba a diseñar el sistema. Del mismo modo se acaró la fiabilidad del sistema.

Posteriormente se realizó una serie de etapas de diseño de circuitos en el programa LTspice. Se buscó este programa por su escalabilidad, su precisión, fácil implementación. En la etapa inicial de diseño se desarrollaron los módulos que fueran totalmente digitales, como es el caso de los comparadores, el contador, el shift register. Esto se realizó de esa forma para luego poder tener un mayor enfoque en los módulos analógicos del sistema. Luego de completar los módulos digitales se realizó una serie de etapas para poder llegar a completar el sistema analógico, para posteriormente terminar el diseño de todo el sistema mixto. Estas etapas son las siguientes: (1) diseño de ADC ideal. (2) Diseño de ADC con opamps ideales. (3) Diseño de ADC final en LTspice, con transistores de 50 nm. (4) Diseño de ADC en Hspice, con tecnología de 50 nm.

El diseño de ADC ideal se refiere a que se implementaron componentes ideales para una elaboración más rápida precisa del sistema. También se buscaba corroborar la arquitectura de forma ideal. En esta etapa se utilizaron fuentes dependientes e independientes, switches y multiplicadores analógicos ideales.

En el momento en que ya existía un sistema completo funcionando, se buscó modificar de forma individual cada módulo analógico, de tal forma que al terminar el diseño de cada módulo el sistema mantendría las mismas entradas y salidas que en la etapa anterior. Se implementaron opamps ideales con los que contaba ya el programa LTspice. Fue necesario rediseñar completamente cada sistema con el fin de acercarse a un diseño final.

Ya con un diseño anterior terminado se cambió el enfoque a la implementación y calibración de opamps utilizando tecnología de 50 nm para reemplazar los transistores ideales utilizados anteriormente. En este proceso fue necesario, en ocasiones, cambiar el diseño anterior o recalibrar el sistema.

Después de la correcta elaboración en el software LTspice, se hace el desarrollo en el software Hspice. Este implementando los modelos respectivos de transistores a usar en el diseño final. En este proceso fue necesario volver a hacer recalibraciones del sistema para poder llegar a tener resultados similares, en exactitud, al anterior proceso.

### VII. Diseño del sistema

En este capítulo se presentará el proceso del diseño de cada módulo, comenzando por los módulos digitales y siguiendo por los analógicos. Es de tomar a consideración que la metodología de diseño es diferente para los módulos digitales y los módulos analógicos. Por lo que el detalle y el procedimiento de diseño que se explicará varia de la misma forma.

## A. Contador digital

Una de las características más importantes del ADC cíclico es que trabaja con un número determinado de etapas, por lo que es necesario tener un circuito que se encargue del conteo de dichas etapas; esta función la lleva a cabo el contador digital.

### 1. Circuitos que componen este módulo

Este circuito esta realizado por subcircuitos, tales como flip-flops, que a su vez han sido realizados por compuertas not y puertas de transmisión (transmission gates). A continuación, se dará una explicación más detallada de los circuitos que se implementan en este módulo.

### a. Compuerta NOT

Este circuito de una entrada y una salida tiene la función de negar una señal digital. De tal modo que, si en su entrada se encuentra un uno lógico, en su salida será un cero lógico o viceversa; esto se puede apreciar mejor en la Tabla No.1.

**Tabla No.1.** Tabla de verdad de compuerta NOT

| INPUT | OUTPUT |  |

|-------|--------|--|

| Α     | NOT A  |  |

| 0     | 1      |  |

| 1     | 0      |  |

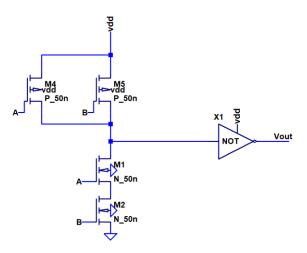

**Figura No.21.** Esquemática compuerta not

Este circuito posee dos transistores, uno tipo PMOS y otro tipo NMOS. En la Figura No.21 se puede apreciar el esquemático de la compuerta NOT. Cabe destacar que en circuitos digitales tipo CMOS es recomendable hacer el transistor pmos más grande que el nmos. Los resultados de este circuito se pueden observar en la Figura No.22.

Figura No.22. Resultados compuerta NOT en LTspice

Estos resultados son los conseguidos con el programa LTspice. A continuación, se presenta la respectiva simulación en Hspice.

**Figura No.23.** Resultados de compuerta not en Hspice. En negro entra del sistema, en rojo salida del sistema.

En figura anterior se puede observar los resultados de la simulación de la compuerta NOT. Se destaca que los tamaños de los transistores son 200nm/50nm, para el transistor PMOS y 100n/50n para el transistor NMOS. Se puede observar en las gráficas que la entrada cambia de un cero lógico a un uno lógico en el tiempo igual a 3 nano segundos, posteriormente la señal de salida cambia, esto retardándose 2 nano segundos, siendo este retardo, para esta aplicación, lo suficientemente corto como para ser considerado despreciable.

Los demás subcircuitos que conlleven compuertas tipo not, implementarán esta configuración. El código de Hspice de la compuerta se presenta en el apéndice B1.

#### b. Puerta de transmisión (transmission gate)

Es un circuito con tres señales de entrada y una señal de salida. Sus entradas son un voltaje de entrada Vi, la señal de control y el negado de esta. En su salida puede tener dos configuraciones, la primera es una alta impedancia y la segunda es copiar el voltaje de entrada Vi. Esto se puede observar en la siguiente tabla.

**Tabla No.2.** Tabla de verdad circuito de puerta de transmisión

| CONTROL |      | INPUT | OUTPUT |

|---------|------|-------|--------|

| pMOS    | nMOS | IN    | OUT    |

| 0       | 1    | 0     | 0      |

|         |      | 1     | 1      |

| 1       | 0    | 0     | z      |

|         |      | 1     |        |

Se hace la mención que este circuito es especialmente útil para el diseño de flipflop tipo D y para el diseño de circuitos analógicos, pues el hecho que pueda tener en ocasiones una salida con alta impedancia permite poder tener más de una entrada conectada en paralelo, lo que permite a un circuito recibir estados de varios circuitos, en diferentes tiempos. Esto se puede observar en la siguiente figura.

**Figura No.24.** Conexión de varios circuitos de entrada a través de puertas de transmisión, diagrama

El funcionamiento de un transmission gate se puede observar en la Figura No.25, donde se conectan dos de estos, con diferentes señales de entrada, a una misma salida. En este caso fue posible usar la misma señal de control luego de negarla, pero en el caso de haber más sistemas interconectados esto no sería posible.

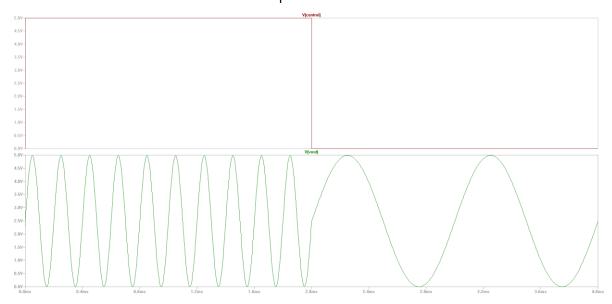

**Figura No.25.** Gráfica de ejemplo de conexión de varios circuitos de entrada a través puertas de transmisión.

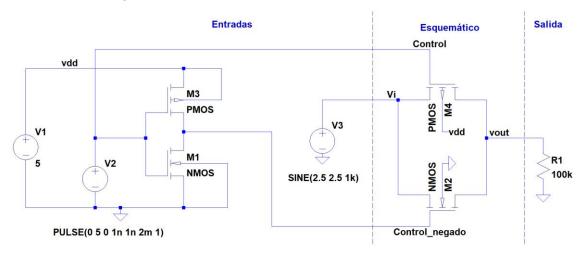

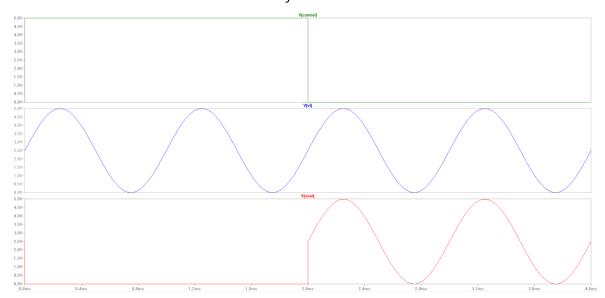

La siguiente figura se muestra el esquemático de una puerta de transmisión, junto con las respectivas entradas y su salida para hacerlo funcionar correctamente y así poder mostrar su funcionamiento como se observa en la Figura No.27.

**Figura No.26.** Esquemático de circuito puerta de transmisión

**Figura No.27.** Resultados, en verde la señal de control, en azul la señal de entrada y en rojo la señal de salida

En este circuito se puede destacar la importancia del tamaño de los transistores. Pues si estos no están bien dimensionados, la salida varía de la entrada, generando un error en el sistema. La Figura No.28 muestra en una misma gráfica la señal de salida y la señal de entrada cuando los transistores tienen la misma dimensión, 32nm/32nm para todos los dos transistores utilizados. Se puede observar como los voltajes mayores no pasan correctamente, son atenuados de forma no lineal. Sin embargo, en la Figura No.29 se puede observar cómo, luego de un correcto dimensionamiento, se puede obtener una salida que se parezca a la entrada respectivamente. En este caso se incrementó el tamaño del ancho (w) del transistor pmos en 1024nm.

**Figura No.28.** Error por dimensionamiento de los transistores en puertas de transmisión, en azul señal de entrada, en rojo señal de salida.

**Figura No.29.** Correcto dimensionamiento de transistores en puertas de transmisión. En azul señal de entrada, en rojo señal de salida.

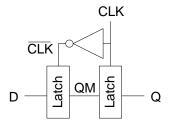

### c. Flip-flop tipo D

Para poder generar un conteo es necesario poder almacenar un estado actual, esto es posible con circuitos tipo flip-flops. Estos guardan un dato hasta que un parámetro de entrada, un flanco positivo, indica que vuelvan a cargar un nuevo valor. Este circuito cuenta con dos señales de entrada y dos señales de salida. Una señal de entrada, llamada D, recibe los datos a guardar en un futuro, otra entrada es la señal de reloj respectivamente, que indica cuando almacenar los datos que recibe la entrada D. Posee dos señales de salida, una es llamada Q, la otra su negado, llamada Qn. Como funciona un flip-flop tipo D es que cuando se da un flanco positivo en la señal de reloj, la salida Q copia lo que había en ese momento en la entrada D.

Este circuito se realizó implementando los circuitos mencionados anteriormente, compuertas NOT y puertas de transmisión. Específicamente 4 puertas de transmisión y 4 compuertas NOT. Existen varios diseños para hacer un flip flop tipo D, pero se optó por esta por su versatilidad y por qué cumple con los requisitos de diseño.

CLK CLK CLK CLK

**Figura No.30.** Esquemático flip-flop tipo D

Figura No.31. Esquemático de un flip flop tipo D a partir de latches

Existen varios tipos de circuitos que almacenan estados, entre ellos se encuentran unos llamados latches, su funcionamiento consiste en almacenar el estado cuando está el CLK en cero lógico, cuando el CLK está en uno lógico, la salida Q copia el estado de la entrada D. Esto se puede observar en la Figura No.32. En la Figura No.31 se puede observar que se implementaron dos de estos circuitos para formar el circuito flip flop tipo D.

**Figura No.32.** Gráfica de funcionamiento de un latch

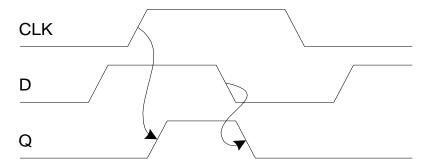

En el momento de escribir el código en Hspice para el flip flop se cometió el error de poner como vdd un voltaje de 5 voltios, esto produjo que la señal de Q se comportara de forma no debida, como se observa en la Figura No.34. Se puede observar que esta no posee cambios bien definidos, sino que tiene cambios parciales y estos se producen en el momento en que CLK y D cambian de flanco. Esto se debe a que el voltaje de V<sub>GS</sub> de los transistores, que seguía siendo de 1.5 V, no llegó a saturar el transistor y entonces la salida de estos no llegó a ser el voltaje de vdd en ningún momento.

Se puede apreciar el correcto funcionamiento de circuito flip flop tipo de D en la Figura No.33. Se hablarán de ciertos puntos específicos de la Figura No.33 para resaltar su correcto funcionamiento. En el tiempo de 3ns se puede observar que la señal de CLK tiene un flanco positivo, en ese momento la señal D, de entrada, estaba en un estado positivo, lo que produce que la señal de salida, Q, tenga un cambio de estado positivo. Luego de eso se puede observar en el tiempo de 5ns como la señal de CLK tiene otro flanco positivo, mientras que en ese momento la señal de entrada D se contaba con un cero lógico, entonces la señal de Q tiene un cambio de estado en ese momento y baja su señal a cero voltios

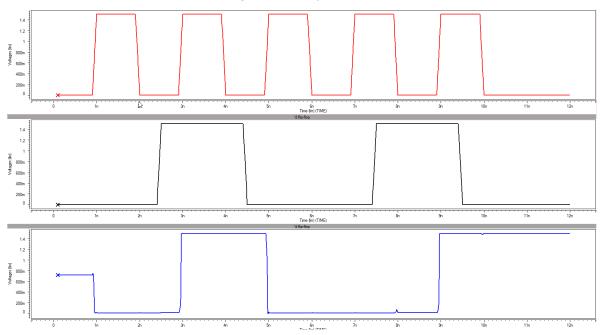

**Figura No.33.** Funcionamiento correcto de flip-flop tipo D. En rojo señal de CLK, en negro señal D y en azul señal Q.

**Figura No.34.** Funcionamiento incorrecto de flip-flop tipo D. En azul señal de CLK, en verde señal D y en rojo señal de Q.

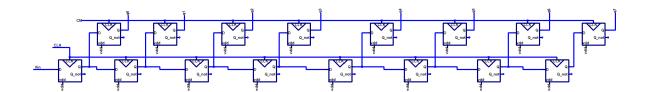

### 2. Contador digital de tres bits

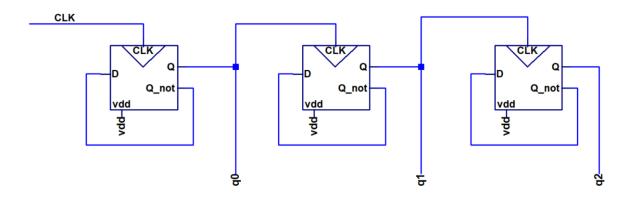

El ADC cíclico realiza la conversión a digital luego de una serie de ciclos de conversión. Estos ciclos son proporcionales a la resolución del ADC. Este ADC maneja una resolución constante a través del tiempo, por lo que es necesario tener un número de ciclos constante por conversión. Para que el circuito conozca el número de ciclos se implementó un contador digital de tres bits.

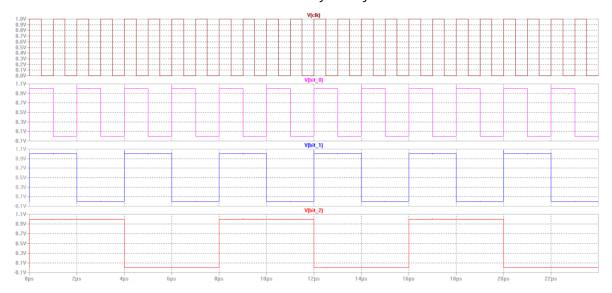

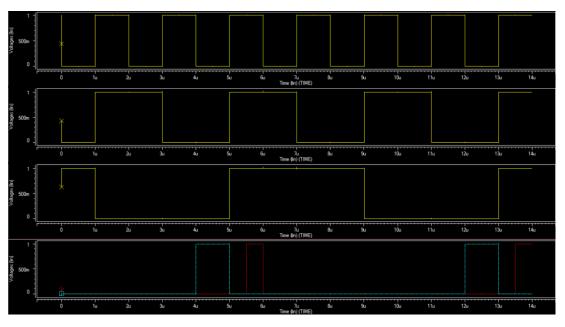

El diseño de un circuito contador de n bits, requiere de la implementación a su vez de n flip-flops. En este caso se realizó de 3 bits, por lo cual se usaron 3 flip-flops. Como se puede apreciar en la Figura No.35, este circuito consiste en dos entradas y tres salidas. Sus entradas son vdd (la alimentación, en este caso es 1V) y clk (el reloj del sistema). Sus salidas son q0, q1, q2 siendo estos los bits de conteo. Y en la Figura No.36 se puede observar las gráficas de las señales de clk y de los bits que llevan el conteo de ciclos.

Figura No.35. Circuito contador de 3 bits

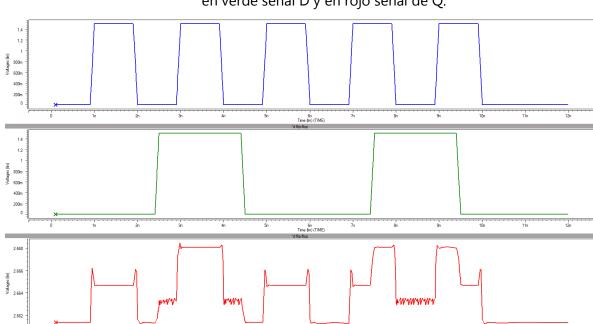

**Figura No.36.** Resultados circuito contador. En corinto señal clk, en rosado bit 0, en azul bit 1 y en rojo bit 2

Se puede observar en la Figura No.36 que el conteo inicia en el número más alto, en este caso el número siete en binario, y que el conteo es descendente, esto debido a que al inicio todos los valores del contador se encuentran en cero (Figura No.37, con reloj desfasado para hacer notar el conteo). La entrada D del flip-flop está conectada a la salida Q\_not, como se observa en la Figura No.35, por lo que todos los bits del contador al recibir el primer flaco positivo de reloj se cambian a uno. La razón por la cual el contador va en descenso tiene que ver con la forma en que están conectados los flip-flops, el hecho que siguen el mismo patrón de estar conectados para que en flanco positivo de la señal, bit, anterior genere un cambio. Posibles soluciones para generar un conteo positivo serían negar todos los bits, o sacarlos del Q\_not del flip-flop, puesto este es el negado de la señal de salida. Otra solución sería que cambiar la lógica del segundo y tercer bit, que los flip-flops cambien en flanco bajo, esto se podría conseguir conectando la salida Q\_not al clk del siguiente flip-flop.

### B. Comparador digital

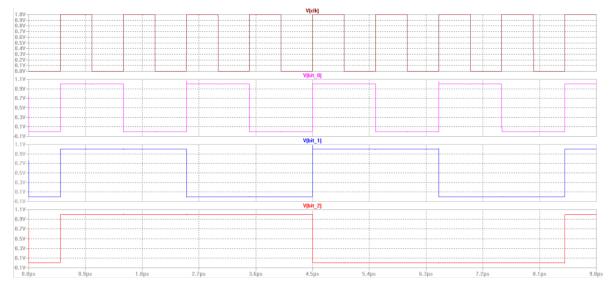

Sabiendo en qué ciclo se encuentra la conversión del ADC, se generan banderas para indicar el momento en el que ocurren ciertos eventos durante el proceso, pues el circuito no es capaz de entender qué etapa de la conversión está sucediendo. Un comparador digital corrobora el estado de las entradas y a través de lógica booleana procesa una señal que representa la realización de cierto acontecimiento esperado. Las entradas de este comparador son estados del sistema, en este caso, los bits de salida del contador, la señal de reloj y las señales de energía, vdd y gnd.

En este caso particular es necesario obtener dos estados, banderas, del comparador. La primera de ellas es la bandera que indica al shift register en qué momento ya terminó el proceso de conversión y es preciso copiar los bits de este a la memoria, llamada en este proyecto como "Copy to Memory". La segunda bandera indica cuando es momento de iniciar una nueva conversión y obtener una muestra a convertir del exterior del circuito, llamada "New sample". En la Figura No.38 se representa conceptualmente este comparador.

Bit 0

Copy to Memory

New Sample

**Figura No.38.** Concepto comparador implementado

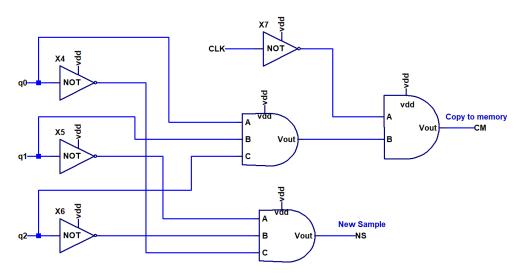

Es posible apreciar el esquemático del circuito comparador en la Figura No.39. Se puede ver que este circuito está compuesto de compuertas not, compuertas AND de tres entradas y compuertas AND de dos entradas.

Figura No.39. Esquemático comparador digital

**Figura No.40.** Esquemático AND de tres entradas

Figura No.41. Esquemático AND de dos entradas

En la Figura No.40 y Figura No.41 se puede observar los esquemáticos de los circuitos AND de tres y dos entradas utilizados para el diseño del comparador digital.

Una de las dificultades presente en este módulo, fue definir en qué momento y duración del ciclo desplegar las banderas para el correcto funcionamiento del circuito. En el caso de la señal llamada "New sample" se definió cuando el contador tenía el valor de siete en binario y contaba con la duración de 1 ciclo. Puesto es una señal que tiene un conteo regresivo se dice que el valor siete en el contador corresponde al primer valor de esa conversión y la bandera funciona alimentando a un transmission gate, mientras esta esté levantada el transmission gate deja pasar la señal deseada al muestreador de señales y tomando en cuenta el funcionamiento de este muestreador de señales, que se explicara posteriormente, la primera señal se muestra en el valor siete del contador, para que sea procesada en el siguiente ciclo.

En el caso de la señal llamada "Copy to Memory" era necesario copiar del shift register a la memoria la señal después de terminar toda la conversión, pero antes de iniciar una nueva conversión, antes de la señal "New sample", esto corresponde al valor cero del contador. El problema que surgió entonces fue que coincidía con la última conversión del

ciclo. Por lo tanto, fue necesario atrasar la señal medio ciclo. Esta señal alimenta a un flipflop, por lo tanto, el flanco de subida es lo importante en esta señal. Se atrasó la señal al pasar la señal de salida con el reloj del sistema a través de un and de dos entradas.

## C. Circuito Shift Register y memoria

El ADC de este trabajo tiene la característica de que proporciona los bits de uno en uno por cada ciclo. Luego de esto es necesario un sistema que tome esos bits de cada ciclo y luego los pase a una memoria donde se mantengan por un periodo de conversión sin cambiar. Este subcircuito es el que proporciona la salida del sistema general, hacia el exterior del circuito, brindando el resultado de la conversión luego de su correcto procesamiento. Sus entradas consisten en diferentes señales: la señal de reloj, la bandera "Copy to memory" (explicada anteriormente), la señal de salida del comparador analógico, la alimentación del sistema (vdd y gnd).

La salida del comparador analógico proporciona la información sobre la conversión de ese ciclo, correspondiente a un bit. Ese bit se guarda por un ciclo en el primer flip-flop, luego en el siguiente ciclo es movido, ese bit de información, al siguiente flip-flop y así por el número de ciclos que constituyen la conversión, en este caso ocho ciclos. En el momento que ya se ha dado la conversión una bandera, llamada "Copy to Memory" indica que toda la información que se ha mantenido en los flip-flops del shift register va a ser movida a un banco de flip-flops que componen una memoria donde se va a guardar la información de conversión por un ciclo de conversión completo. Para luego ser reemplazado por otro valor de conversión de un ciclo posterior. El circuito diseñado enteramente por flip-flops tipo D se observa en la Figura No.42.

**Figura No.42.** Esquemático de circuito shift register y memoria

En los siguientes tres incisos (D, E, F) se postularán los circuitos analógicos implementados en el sistema.

## D. Comparador analógico

Existen varios tipos de ADC, entre los cuales destaca el tipo flash. Este ADC funciona implementando un comparador por cada rango (o estados, explicado en el capítulo anterior) de conversión. En algunos ADCs, la forma de funcionar es identificando entre todos los sub-rangos posibles el valor digital que coincida con el valor analógico de entrada, en este ejemplo se implementan varios comparadores. En otras ocasiones se implementa una forma de conversión iterativa, en la cual se reutiliza el mismo comparador varias veces. En conclusión, el circuito comparador analógico es fundamental en el diseño de convertidores analógicos a digital, independientemente de la arquitectura a utilizar.

El diseño con comparadores analógicos consiste en que se seleccione entre dos o más posibles sub-rangos donde asignar la señal de entrada. Para este trabajo, se introduce una señal que tiene un rango entre 0V y 1V. Se compara si es mayor al valor máximo de comparación divido dos, 0.5V. Si es mayor que este valor el sistema devuelve un valor positivo en binario, correspondiente a 1V. en caso contrario, el sistema devuelve un valor de negativo en binario, que corresponde a 0V. Por lo tanto, la entrada de este sistema es el valor por comparar, el cual viene de la salida del circuito muestreador. La salida del sistema corresponde al valor en binario que representa la iteración correspondiente, funcionan como entrada para los circuitos shift register y el circuito ajustador. En el shift register sirve para procesar el valor de conversión que representa la señal analógica a convertir. En el circuito ajustador sirve para identificar como operar la señal que será procesada en el siguiente ciclo del proceso de conversión.

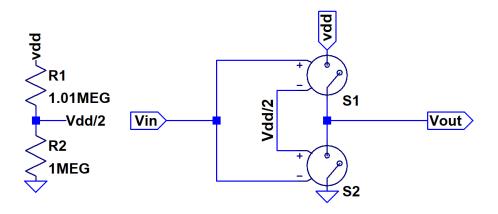

La primera etapa de diseño de este circuito consistió en realizar un circuito que cumpliera con su funcionamiento para probar su implementación, por lo tanto, se realizó un circuito a base de switches ideales en el software LTspice, como se observa en la Figura No.43.

**Figura No.43.** Esquemático de circuito ideal de comparador analógico

If Vin > Vdd/2 ... Vout = vdd... else... Vout = gnd

El funcionamiento del circuito de la Figura No.43 consiste en que, si Vin es mayor que Vdd/2 entonces la salida Vout es igual a vdd, si Vin es menor que Vdd/2 entonces la

salida Vout es igual a gnd. Este diseño contribuyo para corroborar que el este subcircuito junto con los demás circuitos si producían los resultados deseados del sistema. Otro aspecto importante de este circuito fue el poder identificar algunos parámetros necesarios a tomar en cuenta a la hora de modificar este circuito. Ya funcionando todos los sistemas conectados se pasó a la modificación de este circuito.

Se prosiguió a modificar este circuito para realizar uno que tuviera la misma (o lo más parecido posible) función de transferencia, pero implementando opamps diseñados con transistores.

La primera prueba de circuito es el presentado en la Figura No.44. Este circuito no contaba con las características necesarias para ser implementado en el diseño final, era muy lento al momento de hacer un cambio de un 1 lógico a un 0 lógico y viceversa y también otra limitante era que exigía demasiada corriente de entrada por lo que los circuitos que producían la señal de entrada se veían afectados por esto, degradando entonces la señal de entrada del circuito.

**Figura No.44.** Comparador implementando opamp con transistores de 50 nm

Se hizo otra prueba implementando otro circuito amplificador que saturara la señal de entrada, pero del mismo modo que el anterior circuito, este contaba con características

que hacían no factible su implementación, este comparador poseía un gran margen de error en su salida al momento de comparar la señal; otro factor negativo para no tomar en cuenta este diseño fue la potencia y la complejidad que requería éste, no se consideraban óptimas para las características de diseño que este circuito contaba con relación a las que se pretendían obtener.

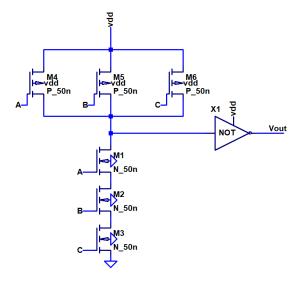

Luego de investigar otros métodos, se llegó a considerar la opción de implementar inversores. Este circuito contaba con mejores características que los anteriores, como la sencillez del diseño. En su implementación en LTspice se diseñaron dos inversores iguales con una relación l/w de ½ para los nmos y ¼ para los pmos.

**Figura No.45.** Circuito comparador usando doble inversor

Posteriormente en el momento de realizar este diseño en Hspice se contó con el problema que la curva, en el análisis AC, del inversor estaba corrida por lo que su punto de comparación estaba desfasado. Otro error que se producía era que en la salida aparecían voltajes no deseados, esto se debía a que la curva debía tener una mayor pendiente. Esto se puede observar en la Figura No.46, donde se puede apreciar como la curva está centrada en 400 mV y la pendiente debe ser mayor para poder tener los resultados requeridos en este diseño.

**Figura No.46.** Análisis AC inversor con error de corrimiento y pendiente en Hspice

Este circuito debe contar con una gran precisión puesto errores en la comparación pueden provocar un resultado totalmente incorrecto en la conversión. Para la correcta calibración de este circuito es necesario ajustar el desfase que posee e incrementar la pendiente de forma significativa. De tal modo que si la señal de entrada de este circuito pasara de los 500mV entonces el comparador lo indicara, de forma precisa, cambiando el valor de su salida.

# E. Circuito sujetador de señales

El circuito sujetador de señales o S/H "Sample and hold" es estrictamente necesario para cualquier tipo de ADC. Para el correcto análisis de datos es necesario poder retener un dato en un intervalo de tiempo, es necesario que el resultado de una conversión permanezca cierto tiempo retenido en su salida.

Entre las entradas que este circuito posee destacan la señal de entrada del exterior y la señal que retorna del circuito ajustador de señales. A través de dos circuitos

transmission gate se elige que señal servirá como entrada, de las dos señales mencionadas anteriormente, en cada ciclo. Al inicio de la conversión, en el primer ciclo, es necesario obtener una muestra del exterior para luego procesarla y obtener de forma recursiva una nueva muestra que servirá para el segundo ciclo, del mismo modo la muestra de este segundo ciclo determina la siguiente muestra. Por lo que se utiliza la entrada del exterior en un ciclo y luego se utiliza la entrada de la señal que retorna del circuito ajustador las siguientes veces por cada conversión que se realice. El que señal dejar pasar esta determinado por una bandera llamada NS "New sample", que indica a los transmission gate que estado tomar en qué momento.

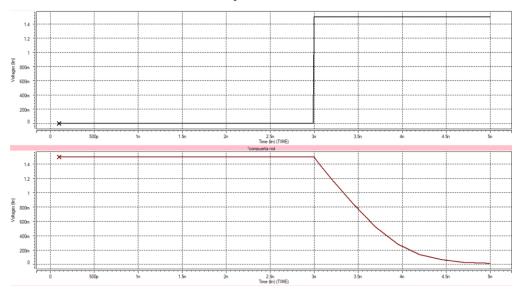

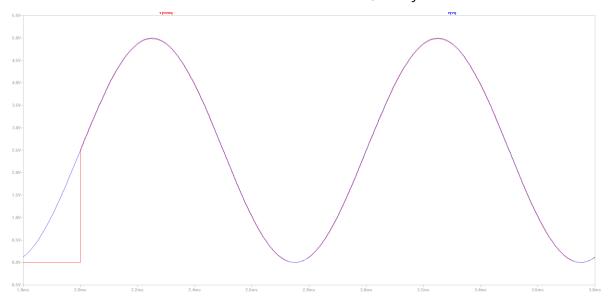

La forma como se realizó el circuito S/H fue implementando dos circuitos T/H. Como se puede observar en la Figura No.47 un circuito Track and hold tiene una etapa llamada "Sample mode", la cual consiste en seguir la señal de entrada, la siguiente etapa llamada "hold mode", consiste en retener la señal cierta cantidad de tiempo. Así mismo se puede observar como un circuito S/H solo retiene la señal por el intervalo de tiempo que dura el ciclo, para luego retener otro intervalo de tiempo. Si luego de contar con un circuito T/H se coloca otro circuito T/H en serie al primero y desfasado en tiempo por medio ciclo, lo que ocurre es que el segundo T/H tiene su etapa de Sample mode mientras que el primer T/H tiene su etapa de Hold mode, para luego el segundo T/H pasara a su etapa de Hold mode, por lo que mantendría la señal retenida, como lo hace un circuito S/H, todo un ciclo completo.

**Figura No.47.** Salida de (a) circuito S/H ideal y (b) circuito track and hold (T/H)

Como se puede observar en la Figura No.48, este circuito está formado por tres amplificadores operacionales, que han sido usados como seguidores de voltaje para poder compensar la corriente que otros circuitos demandarían de los capacitores y así poder hacer que los capacitores cuenten con un voltaje constante cuando es requerido. Se cuenta con cuatro circuitos transmission gate, de los cuales dos de ellos son para determinar cuál va a ser la señal de entrada a ser muestreada. Los otros dos son parte de los dos circuitos T/H utilizados, sirven para aislar los al circuito y así poder mantener el Hold mode que corresponde a cada uno de estos. Dos inversores son utilizados para negar la señal NS y la señal reloj, en el caso de la señal NS se busca que con una bandera controlar dos circuitos que funcionan sincronizados, mientras uno funciona el otro deja de funcionar; en el caso de la señal de reloj invertida sirve para controlar los dos circuitos T/H desfasados medio ciclo. Por último, se cuenta con dos capacitores que sirven para mantener el voltaje en el hold mode.

**Figura No.48.** Esquemático circuito muestreador

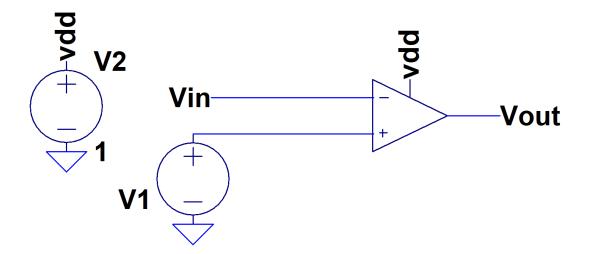

## F. Circuito ajustador de señales

Previamente se ha mencionado que la señal de entrada del ADC se modifica para poder ser reutilizada en futuros ciclos en la conversión. Este circuito modifica la señal analógica muestreada en el circuito S/H de tal forma que puede ser utilizada nuevamente. Este circuito permite poder reutilizar los otros circuitos un número N de ciclos. Hacer un circuito que trate una señal de forma recursiva hace necesario tener que ajustar una futura señal en el momento que se cuenta con la presente señal.

La función de este circuito consiste en operar la señal de tal forma que cumpla con el algoritmo de un ADC cíclico, con esto se refiere a que, dependiendo del tipo de señal en este momento, así será la futura señal por operar. Este circuito cumple con la siguiente ecuación:  $V_{out} = 2V_{in}$ , no obstante dependiendo de una señal proveniente del comparador ( llamada "COMP" en la Figura No.50) la salida del sistema se le restaría un voltaje constante llamado  $V_{CM}$ , de tal forma que  $V_{out} = 2V_{in} - V_{cm}$ , donde  $V_{CM} = V_{dd} = 1$  V. Por lo tanto:

$$V_{out} = \begin{cases} 2 V_{in}, & Si \ COMP = 0V \\ 2V_{in} - V_{cm}, & Si \ COMP = 5V \end{cases}$$

Las entradas de este circuito son la señal proveniente del comparador COMP, los voltajes de alimentación y la señal proveniente del S/H. Este circuito solo cuenta con una salida, esta llega al circuito S/H.

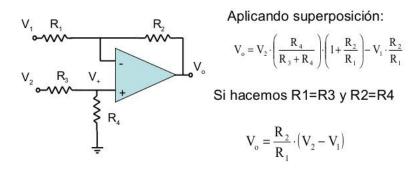

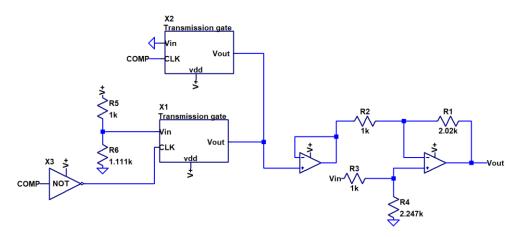

Los subcircuitos que lo conforman son dos transmission gate, dos amplificadores operacionales, un inversor y seis resistencias. Se utilizó un amplificador operacional para formar un circuito restador, se puede observar en la Figura No.49, previo al ajuste del circuito se buscó que R1 = R3 y R2 = R4, de tal modo que este circuito no recibiera Vcm sino Vcm/2 para así hacer que R2 = 2R1, de este modo se cumpliría la función de transferencia requerida por el sistema. Posteriormente se utilizaron dos transmission gate para determinar que si resta Vcm/2 o 0V a la señal, de tal modo que cumpliera con la ecuación antes mencionada. Otro amplificador operacional fue utilizado como seguidor para con este brindar la corriente que necesitara el circuito restador. El inversor se utilizó para controlar los dos transmission gate con una misma señal.

Figura No.49. Circuito restador